## 1 to 16 Decoder

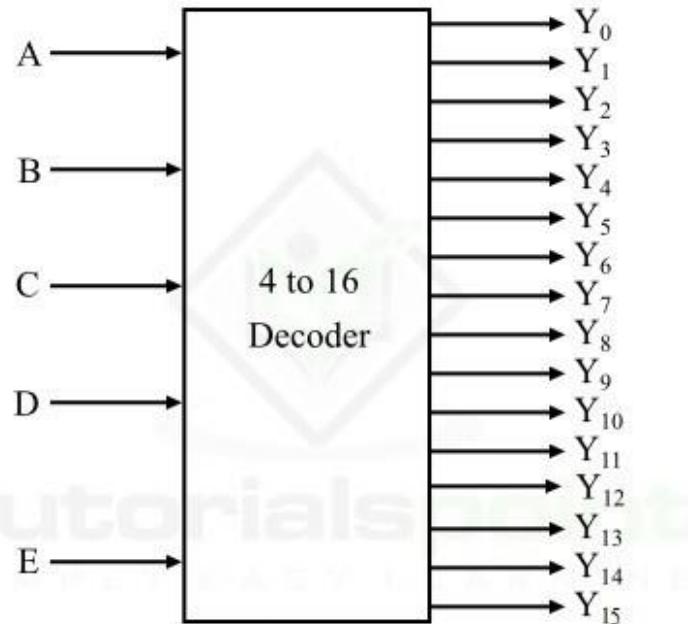

The 4 to 16 decoder is the type of decoder which has 4 input lines and 16 ( $2^{14}$ ) output lines. The functional block diagram of the 4 to 16 decoder is shown in Figure-6.

Figure 6 - 4 to 16 Decoder

When this decoder is enabled with the help of enable input E, it's one of the sixteen outputs will be active for each combination of inputs. The operation of the 4-line to 16-line decoder can be analyzed with the help of its function table which is given below.

| Inputs   |          |          |          |          | Output |

|----------|----------|----------|----------|----------|--------|

| <b>E</b> | <b>A</b> | <b>B</b> | <b>C</b> | <b>D</b> |        |

| 0        | X        | X        | X        | X        | 0      |

| 1        | 0        | 0        | 0        | 0        | $Y_0$  |

| 1        | 0        | 0        | 0        | 1        | $Y_1$  |

|   |   |   |   |   |          |

|---|---|---|---|---|----------|

| 1 | 0 | 0 | 1 | 0 | $Y_2$    |

| 1 | 0 | 0 | 1 | 1 | $Y_3$    |

| 1 | 0 | 1 | 0 | 0 | $Y_4$    |

| 1 | 0 | 1 | 0 | 1 | $Y_5$    |

| 1 | 0 | 1 | 1 | 0 | $Y_6$    |

| 1 | 0 | 1 | 1 | 1 | $Y_7$    |

| 1 | 1 | 0 | 0 | 0 | $Y_8$    |

| 1 | 1 | 0 | 0 | 1 | $Y_9$    |

| 1 | 1 | 0 | 1 | 0 | $Y_{10}$ |

| 1 | 1 | 0 | 1 | 1 | $Y_{11}$ |

| 1 | 1 | 1 | 0 | 0 | $Y_{12}$ |

| 1 | 1 | 1 | 0 | 1 | $Y_{13}$ |

| 1 | 1 | 1 | 1 | 0 | $Y_{14}$ |

| 1 | 1 | 1 | 1 | 1 | $Y_{15}$ |

## Binary Addition

In binary arithmetic, the process of adding two binary numbers is called binary addition. Where, the binary numbers consist of only 0 and 1. In the binary addition, a carry is generated when the sum is greater than 1.

### Rules of Binary Addition

The addition of two binary numbers is performed according to these rules of binary arithmetic –

$$0 + 0 = 0$$

$$0 + 1 = 1$$

$$1 + 0 = 1$$

$$1 + 1 = 10 \text{ (Sum = 0 & Carry = 1)}$$

Let us consider some examples to understand the binary addition.

## Example 1

Add two binary numbers, 1101 and 1110.

## Solution

The binary addition of the given binary numbers is described below –

$$\begin{array}{r} 1 \ 1 \\ 1 \ 1 \ 0 \ 1 \\ + 1 \ 1 \ 1 \ 0 \\ \hline 1 \ 1 \ 0 \ 1 \ 1 \end{array}$$

## Explanation

Add 1 (rightmost bit of first number) and 0 (rightmost bit of the second number). It gives  $1 + 0 = 1$  (thus, write down 1 as sum bit).

Add 0 (second rightmost bit of first number) and 1 (second rightmost bit of the second number). It gives  $0 + 1 = 1$  (write down 1 as sum bit).

Add 1 (third rightmost bit of first number) and 1 (third rightmost bit of second number). It gives  $1 + 1 = 10$  (write down 0 as sum and 1 as carry).

Add 1 (leftmost bit of the first number), 1 (leftmost bit of second number) and 1 (carry). It gives  $1 + 1 + 1 = 11$  (write down 1 as sum and 1 as carry).

Write the end around carry 1 in the sum.

Thus, the result is 11011.

## Example 2

Add 1010 and 11011.

## Solution

The binary addition of given numbers is explained below –

$$\begin{array}{r} 1 \ 1 \\ 1 \ 0 \ 1 \ 0 \\ + 1 \ 1 \ 0 \ 1 \ 1 \\ \hline 1 \ 0 \ 0 \ 1 \ 0 \ 1 \end{array}$$

## Explanation

Add 0 (rightmost bit of first number) and 1 (rightmost bit of second number). It gives  $0 + 1 = 1$  (write down 1 as sum).

Add 1 (second rightmost bit of first number) and 1 (second rightmost bit of second number). It gives  $1 + 1 = 10$  (write down 0 as sum and 1 as carry).

Add 0 (third rightmost bit of first number), 0 (third rightmost bit of second number), and 1 (carry). It gives  $0 + 0 + 1 = 1$  (write down 1 as sum).

Add 1 (leftmost bit of first number) and 1 (second leftmost bit of second number). It gives  $1 + 1 = 10$  (write down 0 as sum and 1 as carry).

Add 1 (leftmost bit of second number) and 1 carry. It gives  $1 + 1 = 10$  (write down 0 as sum and 1 as the end around carry).

Hence, the sum of 1010 and 11011 is 100101.

## Binary Subtraction

In binary arithmetic, binary subtraction is a mathematical operation used to find the difference between two binary numbers. In binary subtraction, each bit of the binary numbers is subtracted, starting from the rightmost bit.

Also, a borrow bit can be taken from higher bits if required.

## Rules of Binary Subtraction

The binary subtraction is performed as per the following rules of binary arithmetic –

$$0 - 0 = 0$$

$$1 - 0 = 1$$

$$0 - 1 = 1 \text{ (borrow 1 from the next higher bit)}$$

$$1 - 1 = 0$$

Let us see some examples to understand the binary subtraction.

## Example 1

Subtract 1100 from 1101.

## Solution

The subtraction of given binary numbers is given below –

$$1101 \ 1100 = 0001$$

$$\begin{array}{r} 1 \ 1 \ 0 \ 1 \\ - 1 \ 1 \ 0 \ 0 \\ \hline 0 \ 0 \ 0 \ 1 \end{array}$$

### Explanation

Subtract 0 (rightmost bit of second number) from 1 (rightmost bit of first number). It gives  $1 - 0 = 1$  (write down 1 as difference).

Subtract 0 (second rightmost bit of second number) from 0 (second rightmost bit of first number). It gives  $0 - 0 = 0$  as result.

Subtract 1 (third rightmost bit of second number) from 1 (third rightmost bit of first number). It gives  $1 - 1 = 0$  as result.

Subtract 1 (leftmost bit of second number) from 1 (leftmost bit of first number). It gives  $1 - 1 = 0$  as result.

Thus, the difference of 1101 and 1100 is 0001.

### Example 2

Subtract 101 from 1111.

### Solution

The subtraction of given binary numbers is explained below –

$$\begin{array}{r} 1 \ 1 \ 1 \ 1 \\ - 1 \ 0 \ 1 \\ \hline 1 \ 0 \ 1 \ 0 \end{array}$$

### Explanation

Subtract rightmost bits:  $1 - 1 = 0$

Subtract second rightmost bits:  $1 - 1 = 0$

Subtract third rightmost bits:  $1 - 1 = 0$

Subtract leftmost bits:  $1 - 0 = 1$

Thus, the result is 1010.

### Example 3

Subtract 1011 from 1101.

### Solution

The binary subtraction of 1101 and 1011 is given below –

$$\begin{array}{r} 010 \\ 1\cancel{1}01 \\ -1011 \\ \hline 0010 \end{array}$$

### Explanation

Subtract rightmost bits:  $1 - 1 = 0$ .

Subtract second rightmost bits:  $0 - 1 = 1$ . A borrow 1 is taken from the next higher bit.

Subtract third rightmost bits:  $0 - 0 = 0$ . The 1 borrow is given to previous bit.

Subtract leftmost bits:  $1 - 1 = 0$ . Thus, the difference of 1101 and 1011 is 0010.

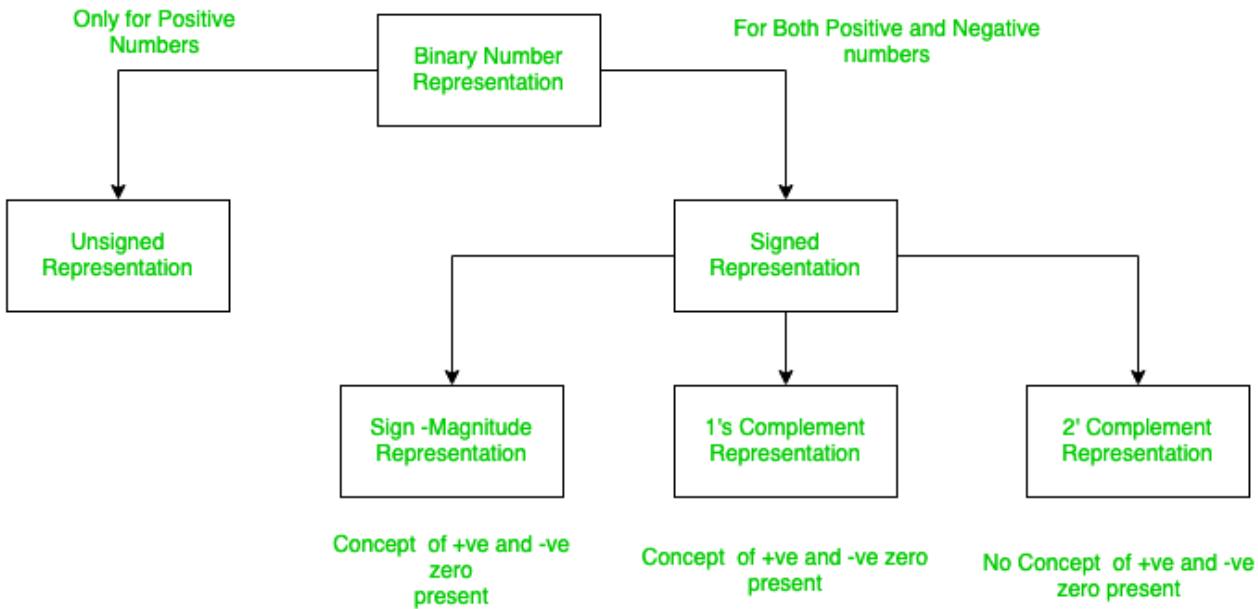

### Unsigned and Signed Numbers Representation in Binary Number System

The binary number system uses only two digits, 0 and 1, to represent all data in computing and digital electronics. Understanding unsigned and signed numbers is important for efficient data handling and accurate computations in these fields.

- The binary system forms the foundation of all digital systems, enabling devices to process and store data.

- Unsigned numbers represent only positive values while signed numbers handle both positive and negative values using methods like two's complement.

- Mastering these concepts is essential for programming, error-free calculations and optimizing system performance.

- Its real-world applications include computer arithmetic, embedded systems and digital signal processing.

## Unsigned Numbers

Unsigned numbers are numeric values that represent only non-negative quantities (zero and positive values). In the binary system, unsigned numbers are represented using only the magnitude of the value, with each bit contributing to its total. The smallest unsigned number is always zero (all bits set to 0), while the maximum value depends on the number of bits used.

### Range of Unsigned Numbers in Binary System:

The range depends directly on the bit length. For an n-bit number:

- Minimum value: 0

- Maximum value:  $2^n - 1$

*Range of unsigned numbers: 0 to  $2^n - 1$*

### Example:

- 4-bit Number: Ranges 0 to 15.

- 8-bit Number: Ranges 0 to 255.

- 16-bit Number: Ranges 0 to 65,535.

### Use Cases of Unsigned Binary Representation:

Unsigned binary numbers serve fundamental roles across computing systems where negative values aren't needed.

- Every byte in RAM gets a unique unsigned address. A 32-bit system can access 4GB of memory (0 to 4,294,967,295).

- RGB color values (0-255) use 8-bit unsigned numbers per channel. Image dimensions and pixel counts also rely on unsigned ranges.

- Microprocessors use unsigned values for status flags and control signals where only positive states exist.

- Packet sizes, port numbers and IP header fields often use unsigned integers to prevent negative interpretations.

- Sensor readings (like temperature or light intensity) and timer counts utilize unsigned formats when negative measurements are impossible.

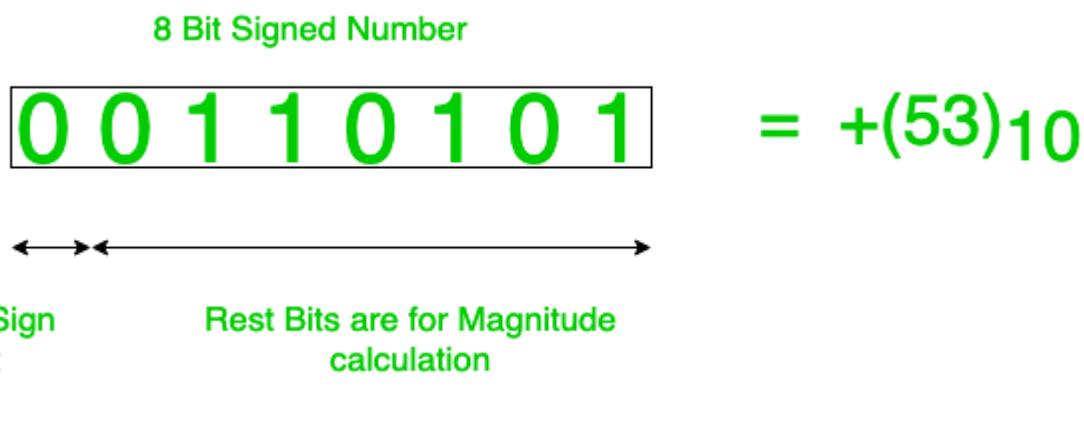

## Sign-Magnitude Representation

This method uses the leftmost bit as a sign flag (0 for positive, 1 for negative) while remaining bits store the absolute value. It creates two zero representations (+0 and -0) and complicates arithmetic operations due to separate sign handling.

### Range of Sign-Magnitude Representation

$-2^{n-1} - 1$  to  $2^{n-1} - 1$

**Example:** In 8-bit system

- Decimal number +25 is represented as 00011001 (Sign bit 0, magnitude 25)

- Decimal number -25 is represented as 10011001 (Sign bit 1, magnitude 25)

Magnitude Representation

### Why Sign-Magnitude Fails in Practice

- Wastes a representable value by encoding both +0 (0000) and -0 (1000), creating unnecessary complexity in comparisons and arithmetic.

- Basic calculations fail because the sign bit requires separate handling. Adding positive and negative versions of the same number doesn't produce zero.

- Requires extra circuitry to manage sign bits during calculations, slowing down processors compared to complement systems.

- Effectively loses one bit of precision since the sign bit doesn't contribute to magnitude, unlike modern systems that use all bits for value representation.

## 2's Complement Representation

2's complement forms negative numbers by inverting all bits of the positive value and adding 1. The leftmost bit serves as the sign indicator while enabling single zero representation. It simplifies hardware design by allowing identical addition and subtraction operations.

**2's complement = 1'complement + 1**

**= (flipping of bits to get 1's complement) + 1**

2's

Complement

### Range of 2's Complement Representation

$-2^{n-1}$  to  $2^{n-1} - 1$

**Example:** In 8-bit system

- *Decimal number +20 is represented as 00010100*

- *Decimal number -20 is represented as 11101100 (Invert bits: 11101011, then add 1)*

### Limitations of 2's Complement

- In a fixed-bit system, 2's complement has a limited range. For an n-bit system, it represents values from  $-2^{n-1}$  to  $2^{n-1} - 1$ , restricting the number of values that can be processed.

- The range for positive numbers is smaller than negative numbers. Negative values range from  $-2^{n-1}$  to  $-1$ , while positive values range from  $0$  to  $2^{n-1} - 1$ , creating an imbalance.

- Overflow occurs when arithmetic operations exceed the representable range, leading to incorrect results.

- Operations like addition and subtraction become complex with sign extension, especially for numbers of different sizes.

- The zero in 2's complement has only one form, while negative numbers have a mirrored representation (e.g.,  $-1$  is 111...1), complicating algorithms like multiplication.

### Arithmetic Operations of 2's Complement Number System

We all know how to perform arithmetic operations of binary number systems. However, computer system generally stores numbers in 2's complement format. So it becomes necessary for us to know how arithmetic operations are done in 2's complement.

#### Addition:

In 2's complement, we perform addition the same as an addition for unsigned binary numbers. The only difference is here we discard the out carry i.e carry from MSB bit as long as the range lies within the accepted range for 2's complement representation.

For eg: Consider a number of bits(n) = 4. So range of numbers will be  $-2^{n-1}$  \space to \space  $2^{n-1}$ , i.e. -8 to 7.

x=2, y=3

addition: 0010

0011

0101

---> +5 in 4 bits

x=-2,y=-3

addition: 1110

1101

1011

---> -5 in 4 bits

(discarding the out carry 1)

In the above examples, there was no overflow as the answers +5 and -5 lie in the range of -8 to 7.

Consider the example,

x=4, y=5

addition: 0100

0101

1001

---> -7 (not in range of -8 to 7)

Hence overflow occurs in the above example as -7 does not exist in the 4bits range.

For more details on overflow, you can refer to the following article [Overflow in Arithmetic Addition in Binary Number System.](#)

## Subtraction

Consider if we have to find the subtraction x-y, we perform the following steps:

1. Take 2's complement of y

2. Add x and 2's complement of y

for eg:

x=3, y=2 for 4 bits 2's complement representation

3---> 0011

Take 2's complement of 2----> 0010

1101 + 1 ---> 1110

Adding 0011 and 1110

0011

1110

0001

---> +1 (discard carry 1 from MSB)

### **Multiplication:**

If operands x and y which need to be multiplied are of n and m digits respectively then the result will be n+m digits. To get correct results we extend digits of both operands to n+m digits

For eg: x=13, y=-6

13 requires 5(m) bits for representation. and -6 requires 4 bits(n) so we will make the bits of 13 and -6 to be equal to  $m+n = 5+4 = 9$

13 -----> 000001101

-6 -----> 111111010

(2's complement of 6)

We then take 2's complement of 110110010 which is 001001110 which is 78. And so 110110010 is -78.

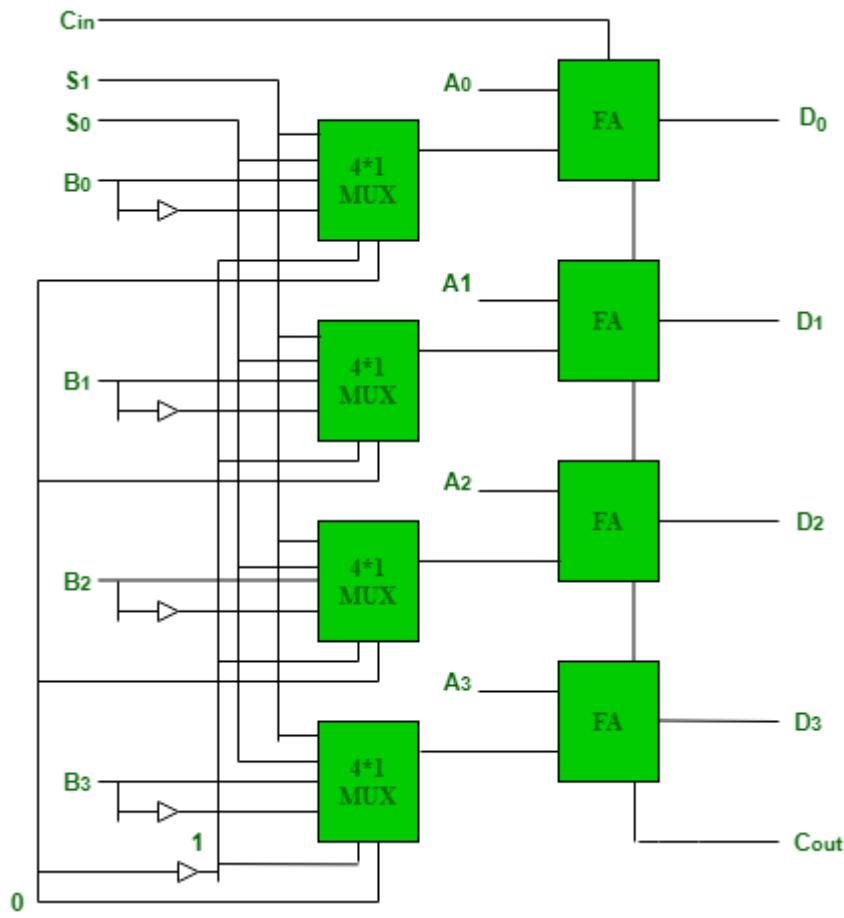

### **Arithmetic Circuit Building blocks**

Arithmetic circuits are fundamental blocks in digital systems and are used for arithmetic operations such as addition, subtraction, multiplication and division. **Arithmetic circuits** can perform seven different arithmetic operations using a single composite circuit.

It uses a full adder (FA) to perform these operations. A multiplexer (MUX) is used to provide different inputs to the circuit in order to obtain different arithmetic operations as outputs.

### **4-Bit Arithmetic Circuit**

Consider the following 4-bit Arithmetic circuit with inputs A and B. It can perform seven different arithmetic operations by varying the inputs of the multiplexer and the carry (C0).

Truth Table for the above Arithmetic Circuit

| S0 | S1 | C0 | MUX Output | Full Adder Output    |

|----|----|----|------------|----------------------|

| 0  | 0  | 0  | B          | $A + B$              |

| 0  | 0  | 1  | B          | $A + B + 1$          |

| 0  | 1  | 0  | $B'$       | $A + B'$             |

| 0  | 1  | 1  | $B'$       | $A + B' + 1 = A - B$ |

| 1  | 0  | 0  | 0          | A                    |

| 1  | 0  | 1  | 0          | $A + 1$              |

| 1  | 1  | 0  | 1          | $A - 1$              |

| 1  | 1  | 1  | 1          | $A - 1 + 1 = A$      |

Hence, the different operations for the inputs A and B are -

1.  $A + B$  (adder)

2.  $A + B + 1$

3.  $A + B'$

4.  $A - B$  (subtrahent)

5.  $A$

6.  $A + 1$  (incrementor)

7.  $A - 1$  (decremental)

### Adder Circuit

Adder circuits are basic arithmetic circuits which are used for binary addition. They come in various types based on their complexity and function. They come in various types based on their complexity and function:

#### 1. Half Adder

A Half adder is the basic type of the adder circuit, which is used in many digital designs. It performs addition of two one-bit binary numbers and generates an output in terms of sum and carry. The [half adder](#) consists of two logic gates: an [XOR gate](#) for the sum and an [AND gate](#) for the carry.

#### 2. Full Adder

A [Full adder](#) is an improvement of the half adder since it performs addition of three binary numbers (two inputs and a carry from the previous addition). It produces a sum and a carry; it is made of two half adders and an OR gate for the carry.

#### 3. Ripple Carry Adder

This kind of adder is made up of more than one full adder cascaded together in a serial manner. The carry output of each full adder is passed to the next; the circuit is simple but carries propagation delay makes it relatively slow.

#### 4. Carry Look-Ahead Adder

Due to the delay issue in ripple carry adders, carry look-ahead adders are built in order to produce carry signals at a faster rate due to increased complexity. They enhance the speed of addition to a very large extent and thus are suitable where high speed processors are required.

### Subtrahent Circuit

Subtrahent circuits perform binary subtraction and come in two primary types: Subtrahent circuits perform binary subtraction and come in two primary types

#### 1. Half Subtrahent

The half subtrahent is used to carry out subtraction with two single bit binary numbers. It produces a difference and a borrow. As in the half adder, the difference is produced using an XOR gate while the borrow is produced using an [AND gate](#) with an inverted input.

#### 2. Full Subtrahent

A full subtrahent extends the half subtrahent to handle three inputs: Two binary numbers and borrow from the foregoing stage. And it produces both a difference and a borrow and the circuit diagram consists of two half subtrahents and an [OR gate](#) for the borrow transfer.

### Multiplier Circuit

Arithmetic circuits include the multiplier circuits which are used to multiply binary numbers. They can be classified into various types based on complexity and speed. They can be classified into various types based on complexity and speed:

### 1. Array Multiplier

An array multiplier employs several adders in an array structure to multiply two binary numbers. They are obtained with the help of AND gates and added subsequent to by using adders.

### 2. Booth Multiplier

Booth's algorithm is used in multiplication of binary numbers that are positive and also negative values. It minimizes the number of partial products and therefore the multiplication is faster than that of the array multiplier.

### 3. Wallace Tree Multiplier

It is a kind of multiplier that uses a tree like structure to minimize on the number of adders needed in the computation of the product of two binary numbers. The Wallace tree multiplier is faster than the other array multipliers because the number of carry propagate is minimized.

## Divider Circuit

Divider circuits perform binary division, and they come in two types. Divider circuits perform binary division, and they come in two types:

### 1. Restoring Divider

The restoring division algorithm works by subtracting the divisor from the remainder and then taking the remainder and continuing the process until the division process is complete. It is less complex than non-restoring division but takes more time than the latter one.

### 2. Non-Restoring Divider

The new algorithm outperforms the restoring division method in that there is no need to restore the remainder at each iteration thus making division faster. Non-restoring dividers are suited best for high speed operation.

Arithmetic circuits are circuits that are used in performing arithmetic operations such as addition subtraction multiplication and division.

# Adders and Subtractors

In digital electronics, **adders** and **subtractors** both are the combinational logic circuits (a combinational logic circuit is one whose output depends only on the present inputs, but not on the past outputs) that can add or subtract numbers, more specifically binary numbers. Adders and subtractors are the crucial parts of arithmetic logic circuits in processing devices like microprocessors or microcontrollers. In this article, we will discuss adders and subtractors in detail.

## What is an Adder?

We have different types of digital devices like computers, calculators that can perform a variety of processing functions like addition, subtraction, multiplication, division, etc. The most basic arithmetic operation that the ALU (arithmetic logic unit) of a computer performs is the **addition** of two or more binary numbers. To perform the operation of addition, a combinational logic circuit, named **Adder** is used.

Adders are classified into two types namely ?

- Half Adder Full

- Adder

A **half-adder** is a combinational logic circuit that performs the addition of only two bits (binary digits). Whereas, a **full-adder** is a combination circuit that performs three bits (binary digits), where two are the significant bits and one is a carry from previous execution.

## What is a Half-Adder?

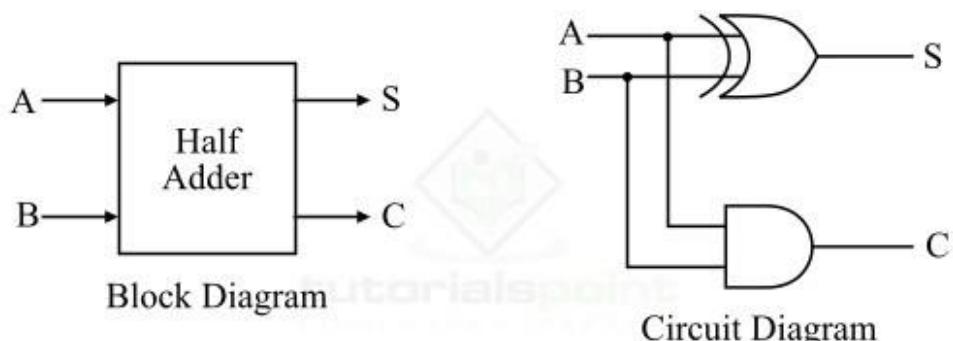

A combinational logic circuit which is designed to add two binary digits is called as a **half adder**. The half adder provides the output along with a carry value (if any). The half adder circuit is designed by connecting an EX-OR gate and one AND gate. It has two input terminals and two output terminals for sum and carry. The block diagram and circuit diagram of a half adder are shown in Figure-1.

Figure 1 - Half Adder

In the case of a half adder, the output of the EX-OR gate is the sum of two bits and the output of the AND gate is the carry. Although, the carry obtained in one addition will not be forwarded in the next addition because of this it is known as half adder.

## Truth Table of Half Adder

The following is the truth table of the half-adder ?

| Inputs |   | Outputs |           |

|--------|---|---------|-----------|

| A      | B | S (Sum) | C (Carry) |

| 0      | 0 | 0       | 0         |

|   |   |   |   |

|---|---|---|---|

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

## Characteristic Equations of Half-Adder

The characteristic equations of half adder, i.e., equations of sum (S) and carry (C) are obtained according to the rules of binary addition. These equations are given below ?

The sum (S) of the half-adder is the XOR of A and B. Thus,

$$\text{Sum, } S = A \oplus B = AB' + A'B$$

The carry (C) of the half-adder is the AND of A and B. Therefore,

$$\text{Carry, } C = A \cdot B$$

## What is a Full Adder?

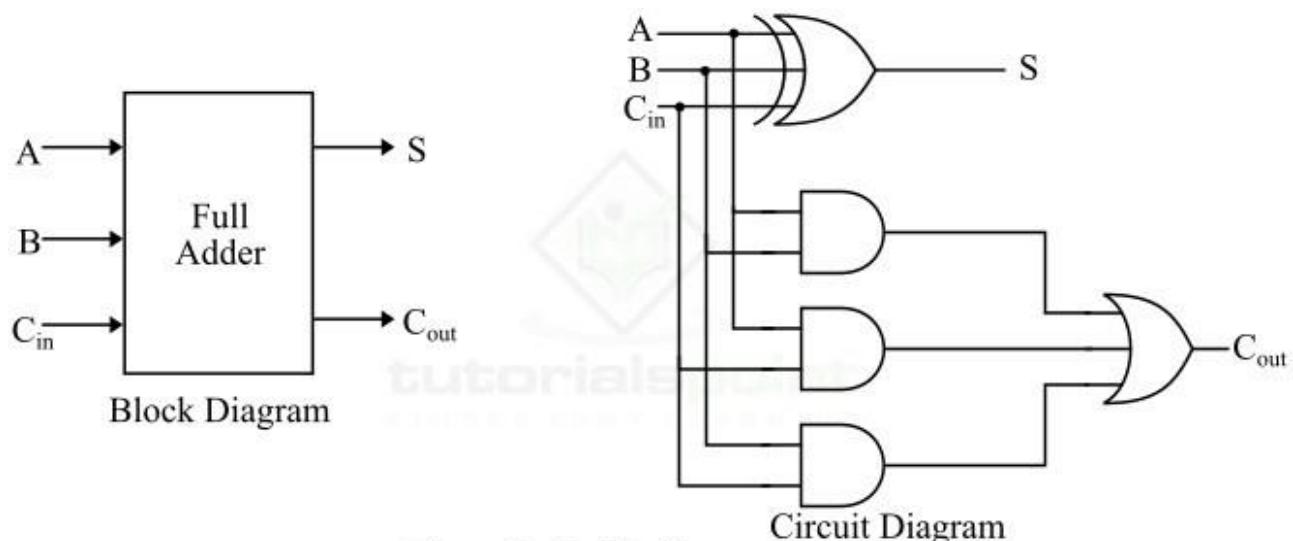

A combinational logic circuit that can add two binary digits (bits) and a carry bit, and produces a sum bit and a carry bit as output is known as a **full-adder**.

In other words, a combinational circuit which is designed to add three binary digits and produces two outputs (sum and carry) is known as a full adder. Thus, a full adder circuit adds three binary digits, where two are the inputs and one is the carry forwarded from the previous addition. The block diagram and circuit diagram of the full adder are shown in Figure-2.

Figure 2 - Full Adder

Hence, the circuit of the full adder consists of one EX-OR gate, three AND gates and one OR gate, which are connected together as shown in the full adder circuit in Figure-2.

## Truth Table of Full Adder

The following is the truth table of the full-adder circuit ?

| Inputs |   |                 | Outputs |           |

|--------|---|-----------------|---------|-----------|

| A      | B | C <sub>in</sub> | S (Sum) | C (Carry) |

| 0      | 0 | 0               | 0       | 0         |

| 0      | 0 | 1               | 1       | 0         |

| 0      | 1 | 0               | 1       | 0         |

| 0      | 1 | 1               | 0       | 1         |

| 1      | 0 | 0               | 1       | 0         |

| 1      | 0 | 1               | 0       | 1         |

| 1      | 1 | 0               | 0       | 1         |

| 1      | 1 | 1               | 1       | 1         |

Hence, from the truth table, it is clear that the sum output of the full adder is equal to 1 when only 1 input is equal to 1 or when all the inputs are equal to 1. While the carry output has a carry of 1 if two or three inputs are equal to 1.

## Characteristic Equations of Full Adder

The characteristic equations of the full adder, i.e. equations of sum (S) and carry output (C<sub>out</sub>) are obtained according to the rules of binary addition. These equations are given below ?

The sum (S) of the full-adder is the XOR of A, B, and C<sub>in</sub>. Therefore,

$$\text{Sum, } S = A \oplus B \oplus C_{in} = A' B' C_{in} + A' B C_{in}' + A B' C_{in}' + A B C_{in}$$

Let us discuss the half-subtractor and full-subtractor in detail.

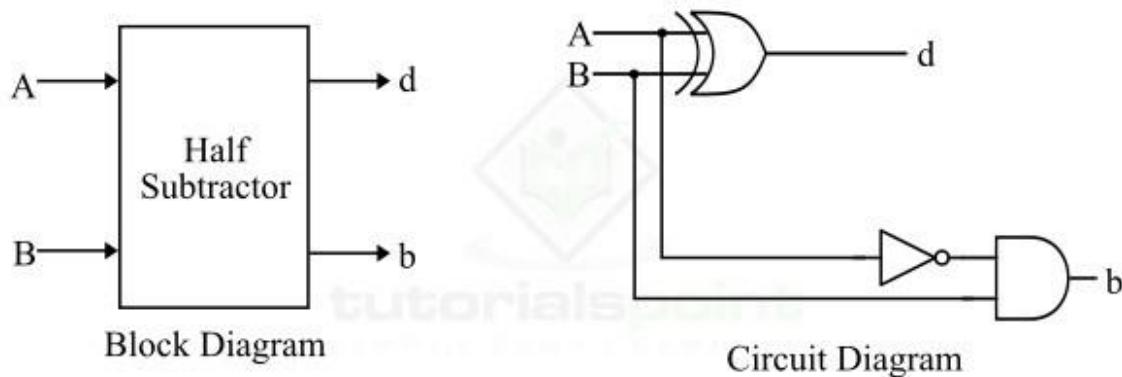

## What is a Half-Subtractor?

A **half-subtractor** is a combinational logic circuit that have two inputs and two outputs (i.e. difference and borrow). The half subtractor produces the difference between the two binary bits at the input and also produces a borrow output (if any). In the subtraction (A- B), A is

called as **Minuend bit** and B is called as Subtrahend bit. The block diagram and logic circuit diagram of the half subtractor is shown in Figure-3.

Figure 3 - Half Subtractor

Hence, from the logic circuit diagram, it is clear that a half subtractor can be realized using an XOR gate together with a NOT gate and an AND gate.

### Truth Table of Half Subtractor

The following is the truth table the half-subtractor ?

| Inputs |   | Outputs        |            |

|--------|---|----------------|------------|

| A      | B | d (Difference) | b (Borrow) |

| 0      | 0 | 0              | 0          |

| 0      | 1 | 1              | 1          |

| 1      | 0 | 1              | 0          |

| 1      | 1 | 0              | 0          |

### Characteristic Equation of Half Subtractor

The characteristic equations of the half subtractor, i.e. equations of the difference (d) and borrow output (b) are obtained by following the rules of binary subtraction. These equations are given below ?

The difference (d) of the half subtractor is the XOR of A and B. Therefore,

$$\text{Difference, } d = A \oplus B = A' B + A B'$$

The borrow (b) of the half subtractor is the AND of A' (compliment of A) and B. Therefore,

$$\text{Borrow, } b = A' B$$

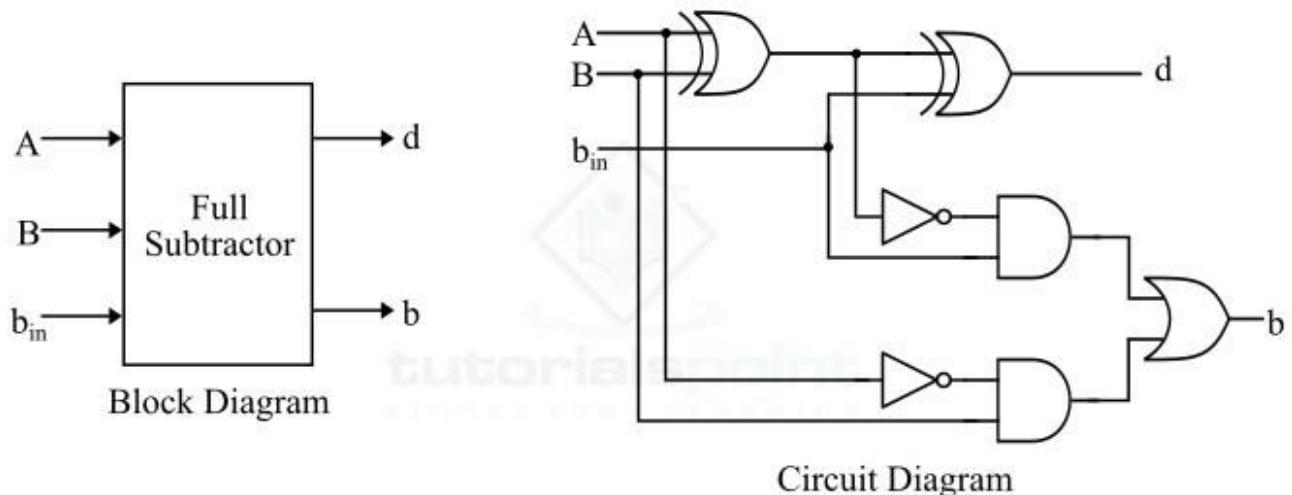

# What is a Full-Subtractor?

A **full-subtractor** is a combinational circuit that has three inputs A, B,  $b_{in}$  and two outputs d and b. Where, A is the minuend, B is subtrahend,  $b_{in}$  is borrow produced by the previous stage, d is the difference output and b is the borrow output.

Since, the half subtractor can only be used to find the difference of LSBs (Least Significant Bits) of two binary numbers. Thus, if there is any borrow during the subtraction of the LSBs, it will affect the subtraction of the next bits of numbers. To overcome this problem of the half subtractor, a full subtractor is realized. The block diagram and circuit diagram of a full-subtractor is shown in Figure-4.

Figure 4 - Full Subtractor

Therefore, we can realize the full-subtractor using two XOR gates, two NOT gates, two AND gates, and one OR gate.

## Truth Table of Full-Subtractor

The following is the truth table of the full-subtractor ?

| Inputs |   |          | Outputs        |            |

|--------|---|----------|----------------|------------|

| A      | B | $b_{in}$ | d (Difference) | b (Borrow) |

| 0      | 0 | 0        | 0              | 0          |

|   |   |   |   |   |

|---|---|---|---|---|

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

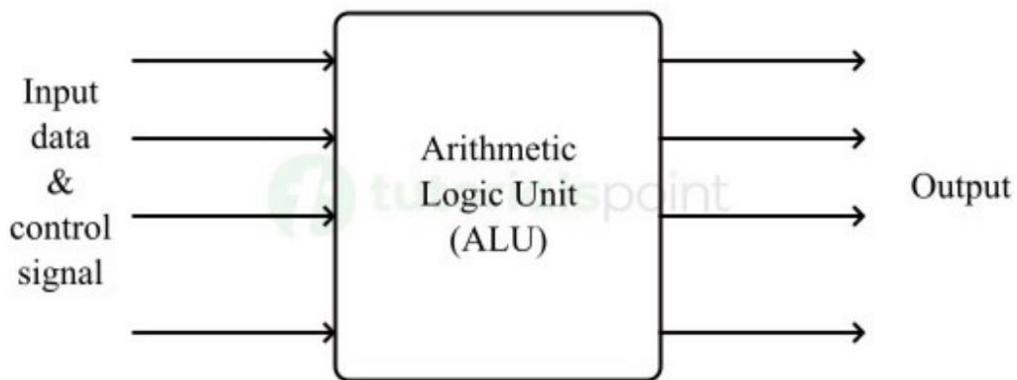

The **Arithmetic Logic Unit (ALU)** is the fundamental component in a computing system like a computer. It is basically the actual data processing element within the central processing unit (CPU) in a computing system. It performs all the arithmetic and logical operations and forms the backbone of modern computer technology.

In this chapter, we will explain the working of the arithmetic logic unit, along with its main components, their functions, and the importance of the ALU in the field of digital system designs.

## What is Arithmetic Logic Unit?

Arithmetic Logic Unit abbreviated as ALU is considered as the engine or heart of every central processing unit (CPU). ALU is basically a combination logic circuit that can perform arithmetic and logical operation on digital data (data in binary format). It can also execute instructions given to a computing system like a digital computer.

Within the complex architecture of a digital computing system, the arithmetic logic unit or ALU plays an important role as it executes and processes all the instructions, performs calculations, manipulates binary data, and performs various decision-making operations.

The development of arithmetic logic unit begins with the need for efficient, high speed, and accurate data processing and computation. With the advancement in electronics technologies, ALU has become a highly sophisticated digital data processing device that can handle a large number of complex instructions and computational tasks.

Today's ALU provides high accuracy, precision, and significantly fast processing speed in computing operations.

### Features of Arithmetic Logic Unit

Here are some key features of arithmetic logic unit –

- The ALU can perform all arithmetic and logic operations such as addition,

subtraction, multiplication, division, logical comparisons, etc.

- It can also perform bitwise and mathematical operations on binary numbers.

- It contains two segments namely, AU (**arithmetic unit**) and LU (**logic unit**) to perform arithmetic operations and logical operations respectively.

- It is the computational powerhouse within a central processing unit (CPU).

- ALU is the part of every CPU where actual data processing takes place.

- ALU is responsible for interpreting the code instructions based on which operations to be performed on the input data.

- Once the data processing is completed, the ALU sends the outcomes to the memory unit or output unit.

## Main Components of Arithmetic Logic Unit

The arithmetic logic unit consists of various functional parts that are responsible for performing specific operations like addition, subtraction, multiplication, division, comparison, and more. Some of the key components of the arithmetic logic unit are explained below –

### Arithmetic Unit

The main components used in the arithmetic unit (AU) segment of the arithmetic logic unit are as follows –

#### Adder

The adder or binary adder is one of the important components of the arithmetic logic unit. It performs the addition of two or more binary numbers. To accomplish this operation, it performs a series of logical and arithmetic operations. Some common types of adders used in the arithmetic logic unit are half-adder, full-adder, parallel adder, and ripple carry adder. Each type of adder is designed and optimized to perform a specific computing operation.

#### Subtractor

The subtractor is another digital combinational circuit designed to perform subtraction of binary numbers. In most arithmetic logic unit, the subtractor uses 2s complement arithmetic to perform subtraction on binary numbers.

#### Multiplier and Divider

In more complex and advanced arithmetic logic units, dedicated multiplier and divider circuits are also implemented to perform multiplication and division on binary numbers. These circuits use advanced processing techniques like iterative or parallel processing to

accomplish these operations.

## Logic Unit

The logic unit (LU) of the ALU comprises the components responsible for performing Boolean or comparison operations. The following are some main components of the logic unit of an ALU –

## Logic Gates

The logic gates like AND, OR, NOT, NAND, NOR, XOR, and XNOR are the key components of logic unit. These are standard logic circuits that can manipulate input data based on some predefined logical instructions and generate a desired output.

Each logic gate can perform a specific logical operation. However, different types of logic gates can be connected together in a specific manner to perform complex logical operations.

## Type of Logic Gate

The brief overview of each type of logic gate is explained here –

- **AND Gate** – It performs the Boolean multiplication on input binary data. Its output is logic 1 or true, only when all its inputs are logic 1 or true.

- **OR Gate** – The OR gate performs the Boolean addition of input binary data. It generates a logic 1 or true output, if any of its inputs is logic 1 or true.

- **NOR Gate** – The NOT gate performs the inversion operation. It gives a logic 1 or true output when its input is logic 0 or false and vice-versa.

- **NAND Gate** – The NAND gate performs the NOTed AND operation and produces a logic 1 or true output when both inputs or any of the inputs is logic 0 or false.

- **NOR Gate** – The NOR gate performs the NOTed OR operation and generates a logic 1 or true output when all its inputs are logic 0 or false.

- **XOR Gate** – The XOR gate performs the exclusive OR operation and produces a logic 1 or true output when its both inputs are dissimilar. Hence, it is used as inequality detector.

- **XNOR Gate** – The XNOR gate performs the exclusive NOR operation and gives a logic 1 or true output when both its inputs are similar. Thus, it is used as an equality detector.

This is all about structure and components of the arithmetic logic unit. Let us now understand what functions an ALU can perform.

# Functions of Arithmetic Logic Unit

The arithmetic logic unit can perform a wide range of functions and operations in digital computing systems. Some important functions that an arithmetic logic unit perform are explained below –

## Arithmetic Operations

The arithmetic operations are one of the primary functions that the arithmetic logic unit performs. This category of operations includes addition, subtraction, multiplication, and division of binary numbers. All these operations form the basis of mathematical computations that the arithmetic logic unit can perform.

## Logical Operations

The arithmetic logic unit can also perform various logical operations such as AND operation, OR operation, NOT operation, etc. These logical operations form the basis of decision making and data manipulation processes.

## Comparison Operations

The arithmetic logic unit also facilitates to perform various comparison operations such as equal to, not equal to, less than, greater than, etc. These comparison operations are essential in decision making processes.

## Shift Operations

The arithmetic logic unit can also perform shift operations on binary numbers such as left shift and right shift. These operations are important in multiplication and division operations. The shift operations can manipulate binary data at bit level and hence optimize the arithmetic calculations.

# Working of Arithmetic Logic Unit

The working of the arithmetic logic unit depends on a combination of input data and control signals. In other words, the arithmetic logic unit receives the input data and control signals and then interpret these data and signals to perform specific operations.

Let us understand the working of the arithmetic logic unit in detail by breaking it down in sub-components.

## Receiving Input Data and Control Signals

The arithmetic logic unit receives the input data from the user and a set of control

signals that specifies the operation to be performed. The data is received through the input data path while the control signals are received from the control unit.

## Execution of Operation

Once the arithmetic logic unit received the input data and control signals, it selects an appropriate functional component among arithmetic unit, logic unit, comparison unit, or shift unit to perform the specific operation. Once the operation completes, the ALU sends the results to the memory unit for storage or output unit.

## Significance of Arithmetic Logic Unit

In the field of digital electronics and computing technology, the arithmetic logic unit plays an important role because of the following reasons –

- It can perform the arithmetic, logical, and comparison operations with very high accuracy, precision, and efficiency.

- It can also perform complex data processing and decision-making operations.

- ALU can execute complex processing tasks at a very high speed that results in better performance and higher efficiency.

## Binary Multiplication

In binary arithmetic, binary multiplication is the process of multiplying two binary numbers and obtain their product.

In binary multiplication, we multiply each bit of one binary number by each bit of another binary number and then add the partial products to obtain the final product.

## Rules of Binary Multiplication

The multiplication of two binary numbers is performed as per the following rules of binary arithmetic –

$$0 \times 0 = 0$$

$$0 \times 1 = 0$$

$$1 \times 0 = 0$$

$$1 \times 1 = 1$$

It is clear that the binary multiplication is similar to the decimal multiplication. Let us

understand the binary multiplication with the help of solved examples.

### Example 1

Multiply 1101 and 11.

### Solution

The binary multiplication of given numbers is described below –

$$\begin{array}{r} 1 \ 1 \ 0 \ 1 \\ \times \ 1 \ 1 \\ \hline 1 \ 1 \ 1 \ 0 \ 1 \\ 1 \ 1 \ 0 \ 1 \\ \hline 1 \ 0 \ 0 \ 1 \ 1 \ 1 \end{array}$$

### Explanation

Multiply the rightmost bit of the second number, 1 by each bit of the first number

Now, shift the partial product one position to the left to perform the next multiplication.

(1101).

Multiply the leftmost bit of the second number, 1 by each bit of the first number (1101).

Finally, sum up all the partial products to obtain the final product.

Hence, the product of 1101 and 11 is 100111.

### Example 2

Multiply 11011 and 110.

### Solution

The multiplication of given binary numbers is demonstrated below –

$$\begin{array}{r} 1 \ 1 \ 0 \ 1 \ 1 \\ \times \ 1 \ 1 \ 0 \\ \hline 1 \ 0 \ 0 \ 0 \ 0 \ 0 \\ 1 \ 1 \ 1 \ 0 \ 1 \ 1 \\ 1 \ 1 \ 0 \ 1 \ 1 \\ \hline 1 \ 0 \ 1 \ 0 \ 0 \ 0 \ 1 \ 0 \end{array}$$

## Explanation

Multiply rightmost bit of the second number (0) by each bit of the first binary number (11011). Shift the partial product one position to the left.

Multiply the second rightmost bit of the second number (1) by each bit of the first binary number (11011).

Again, shift the partial product one position to the left.

Multiply the leftmost bit of the second number (1) by each bit of the first number.

Then, sum up all the partial products to obtain the final product.

Hence, the product of 11011 and 110 is 10100010.

## Binary Division

Binary division is one of the basic arithmetic operations used to find the quotient and remainder when dividing one binary number by another.

### Rules of Binary Division

The following rules of binary arithmetic are utilized while dividing one binary number by another –

$$0 \div 0 = \text{Undefined}$$

$$0 \div 1 = 0 \text{ with Remainder} = 0$$

$$1 \div 0 = \text{Undefined}$$

$$1 \div 1 = 1 \text{ with Remainder} = 0$$

### Binary Division Procedure

- Start dividing from the leftmost bits of the dividend by the divisor.

- Multiply the quotient obtained by the divisor and subtract from the dividend.

- Bring down the next bits of the dividend and repeat the division process until all the bits of given divided are used.

Let us consider some solved examples to understand the binary division.

### Example 1

Divide 110011 by 11.

### Solution

The division of the given binary numbers is explained below –

$$110011 \div 11 = 10001$$

$$\begin{array}{r} 1\ 0\ 0\ 0\ 1 \\ 1\ 1 ) 1\ 1\ 0\ 0\ 1\ 1 \\ \underline{1\ 1} \quad \downarrow \quad \downarrow \quad \downarrow \quad \downarrow \\ 0\ 0\ 0\ 1\ 1 \\ \underline{1\ 1} \\ 0 \end{array}$$

In this example of binary division, the quotient obtained is 10001 and the remainder is 0.

### Example 2

Divide 11011 by 10.

## Solution

The binary division of 11011 by 10 is explained below –  $11011 \div 10 = 1101$

$$\begin{array}{r} 1\ 1\ 0\ 1 \\ 1\ 0 ) \overline{1\ 1\ 0\ 1\ 1} \\ 1\ 0 \downarrow \\ \hline 1\ 0 \downarrow \\ 0\ 1\ 1 \\ \hline 1\ 0 \\ \hline 1 \end{array}$$

Arithmetic Circuits Using HDL

## 1. Introduction

- Arithmetic circuits are **combinational circuits** that perform mathematical operations.

- They are the backbone of processors' **Arithmetic Logic Unit (ALU)**.

- Common operations: **Addition, Subtraction, Multiplication, Division**.

- Designed using **HDL (Hardware Description Language)** → Verilog/VHDL.

---

## 2. Half Adder

**Definition:**

- A **Half Adder** adds two **single-bit binary numbers** (A and B).

- It has two outputs: **Sum (S)** and **Carry (Cout)**.

**Truth Table:**

**A B Sum (S) Carry (Cout)**

|   |   |   |   |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

**Expressions:**

- **Sum =  $A \oplus B$**

- **Carry =  $A \cdot B$**

**Block Diagram (explained):**

- Inputs: A, B

- XOR gate → gives Sum

- AND gate → gives Carry

## HDL (Verilog):

```

module half_adder (input A, B, output Sum, Carry);

assign Sum = A ^ B;

assign Carry = A & B;

endmodule

```

---

## 3. Full Adder

### Definition:

- A **Full Adder** adds **three inputs**: A, B, and Carry-in (Cin).

- Outputs: **Sum (S)** and **Carry-out (Cout)**.

### Truth Table:

A B Cin Sum Cout

|   |   |   |   |   |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 |

### Expressions:

- $\text{Sum} = A \oplus B \oplus \text{Cin}$

- $\text{Cout} = (A \cdot B) + (\text{Cin} \cdot (A \oplus B))$

### Block Diagram:

- Two Half Adders + One OR gate.

### HDL:

```

module full_adder (input A, B, Cin, output Sum, Carry);

assign Sum = A ^ B ^ Cin;

assign Carry = (A & B) | (Cin & (A ^ B));

endmodule

```

---

## 4. Ripple Carry Adder (RCA)

## Definition:

- An **n-bit adder** made by cascading **n Full Adders**.

- Carry-out of one FA → Carry-in of the next.

## Limitation:

- **Slow** due to carry propagation delay.

## HDL (4-bit RCA):

```

module ripple_adder_4bit (input [3:0] A, B, input Cin, output [3:0] Sum, output Cout);

wire C1, C2, C3;

full_adder FA0 (A[0], B[0], Cin, Sum[0], C1);

full_adder FA1 (A[1], B[1], C1, Sum[1], C2);

full_adder FA2 (A[2], B[2], C2, Sum[2], C3);

full_adder FA3 (A[3], B[3], C3, Sum[3], Cout);

endmodule

```

---

## 5. Carry Look-Ahead Adder (CLA)

### Concept:

- To overcome RCA delay, use **Generate (G)** and **Propagate (P)** signals.

- $P_i = A_i \oplus B_i$ ,  $G_i = A_i \cdot B_i$

- Carry generated faster using logic equations.

### Advantage:

- Much **faster** than RCA.

---

## 6. Subtractor Circuits

### Half Subtractor:

- Inputs: A, B

- Outputs: **Difference (D)**, **Borrow (Bout)**

- Equations:

- $D = A \oplus B$

- $Bout = A' \cdot B$

### Full Subtractor:

- Inputs: A, B, Bin

- Outputs: Difference (D), Borrow-out (Bout)

- Equations:

- $D = A \oplus B \oplus Bin$

- $Bout = (A' \cdot B) + (Bin \cdot (A \oplus B)')$

### Using Adders (2's complement method):

- Subtraction  $A - B = A + (2's \text{ complement of } B)$ .

---

## 7. Multipliers

- **Array Multiplier**: shift-and-add method.

- **Booth's Multiplier**: efficient for signed binary multiplication.

- Implemented in HDL using loops and adders.

---

## 8. Dividers

- Implemented using **restoring / non-restoring division algorithms**.

- HDL often uses **iterative subtraction**.

---

## 9. Arithmetic Logic Unit (ALU)

### Definition:

- ALU combines **arithmetic and logic operations**.

- Controlled by **select lines**.

### Typical Operations:

- ADD, SUB, AND, OR, XOR, NOT, INC, DEC, SHIFT.

### HDL (4-bit ALU):

```

module ALU (

input [3:0] A, B,

input [2:0] Sel,

output reg [3:0] Result,

output reg Carry

);

always @(*) begin

case(Sel)

3'b000: {Carry, Result} = A + B; // Addition

3'b001: {Carry, Result} = A - B; // Subtraction

3'b010: Result = A & B; // AND

3'b011: Result = A | B; // OR

3'b100: Result = A ^ B; // XOR

3'b101: Result = ~A; // NOT

3'b110: Result = A + 1; // Increment

3'b111: Result = A - 1; // Decrement

endcase

end

endmodule

```

---

## 10. Advantages of HDL for Arithmetic Circuits

- **Abstract design** (no gate-level wiring needed).

- **Reusable modules** (adders, subtractors).

- **Simulation & testing** possible before hardware.

- **Easily scalable** (4-bit → 8-bit → 32-bit).

- **Synthesis** on FPGA/ASIC.

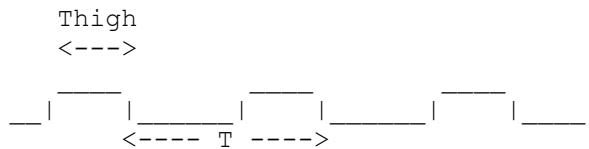

# Clock Waveforms

---

## 1. Introduction

- A **clock signal** is a special digital waveform used to **synchronize** operations in sequential circuits (flip-flops, counters, registers, processors).

- Acts as a **timing reference** for when data should be sampled, stored, or transferred.

- Clock signals are usually **periodic square waves** alternating between logic HIGH (1) and logic LOW (0).

---

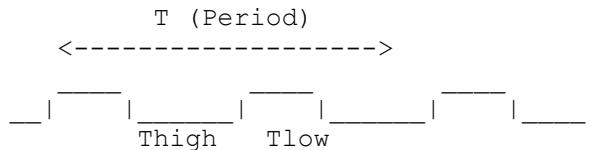

## 2. Characteristics of Clock Waveforms

1. **Period (T):**

- Time taken for one complete cycle (High + Low).

- Measured in seconds.

2. **Frequency (f):**

- Number of cycles per second.

- Formula:

$$f = \frac{1}{T}$$

- Measured in Hertz (Hz).

3. **Duty Cycle (D):**

- Percentage of time clock stays HIGH in one cycle.

- Formula:

$$D = \frac{T_{\text{high}}}{T} \times 100\%$$

4. **Rise Time (tr):**

- Time taken for the clock to rise from logic LOW (0) to logic HIGH (1).

5. **Fall Time (tf):**

- Time taken for the clock to fall from HIGH (1) to LOW (0).

6. **Clock Skew:**

- The time difference when the same clock signal reaches different parts of a circuit.

---

## 3. Types of Clock Waveforms

### 1) Square Wave Clock

- Most common clock signal.

- HIGH and LOW times are equal (50% duty cycle).

- Used in synchronous digital systems.

---

### 2) Rectangular Clock (Variable Duty Cycle)

- HIGH and LOW times are not equal.

- Duty cycle may be >50% or <50%.

---

### 3) Pulse Clock

- A very short HIGH pulse followed by long LOW time.

- Used in triggering flip-flops or control signals.

---

### 4) Triangular / Sawtooth Waveform (Analog Clocks)

- Rarely used in digital logic but common in communication systems.

- Slope increases and decreases linearly.

---

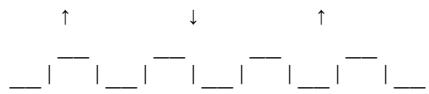

## 4. Clock in Sequential Circuits

- **Edge Triggering:**

- Flip-flops respond to **edges** of clock:

- **Positive Edge (↑):** Transition from LOW → HIGH.

- **Negative Edge (↓):** Transition from HIGH → LOW.

- **Level Triggering:**

- Flip-flops respond while clock is HIGH or LOW (not just at edges).

---

## 5. HDL Representation of Clock

In **Verilog HDL**, clock signals are often generated in testbenches for simulation.

Example (10 ns period clock):

```

module testbench;

reg clk;

initial begin

clk = 0;

forever #5 clk = ~clk; // toggles every 5ns → period = 10ns

end

endmodule

```

---

## 6. Applications of Clock Waveforms

- Synchronization in **processors** (CPU clock).

- Driving **counters, registers, flip-flops**.

- Controlling **timing of data transfer** in buses.

- Used in **communication protocols** (I<sup>2</sup>C, SPI, UART).

## 1. Clock with Period & Frequency

$$f = 1/T$$

- $T = T_{high} + T_{low}$

- $f = 1/T$

## 2. Duty Cycle Illustration

$$\text{Duty Cycle (D)} = (T_{high} / T) \times 100\%$$

- **Thigh** = Time clock is HIGH

- **T** = Total period

## 3. Positive and Negative Edge

Positive Edge ( $\uparrow$ )  $\rightarrow$  LOW to HIGH

Negative Edge ( $\downarrow$ )  $\rightarrow$  HIGH to LOW

## 4. Level Triggering

HIGH-Level Triggering

Triggered while clock = HIGH

LOW-Level Triggering

Triggered while clock = LOW

## 5. Types of Clock Waveforms

### (a) Square Wave (50% Duty Cycle)

### (b) Rectangular Wave ( $\neq$ 50% Duty Cycle)

### (c) Pulse Clock

## TTL Clock

### 1. Introduction to Clock in Digital Logic

- A **clock** is a signal that oscillates between HIGH and LOW states at regular intervals.

- It provides the **timing reference** for synchronous digital systems.

- Without a clock, flip-flops, counters, and sequential circuits cannot function correctly.

---

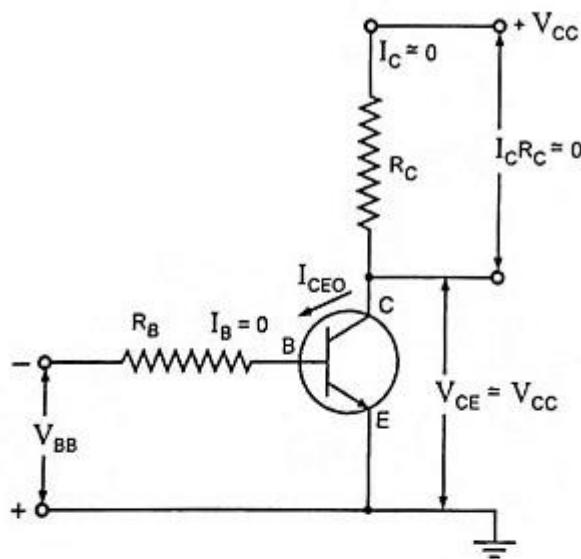

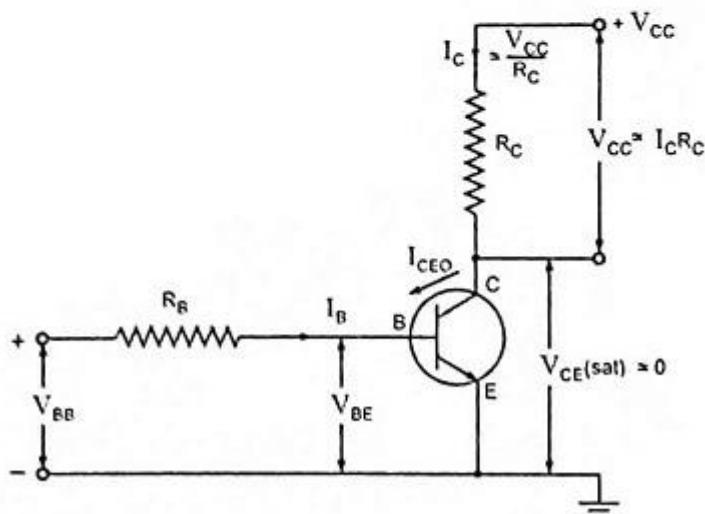

### 2. TTL (Transistor–Transistor Logic) Basics

- **TTL Logic** is a type of digital circuit built using **bipolar junction transistors (BJTs)**.

- It uses a supply voltage of **+5V (standard)**.

- Logic levels in TTL:

- **Logic HIGH (1)**  $\approx$  2V to 5V (typically 5V)

- **Logic LOW (0)**  $\approx$  0V to 0.8V (typically 0V)

- TTL is widely used in digital IC families like **74-series ICs**.

---

### 3. TTL Clock Signal

- A **TTL Clock** is a square waveform that alternates between 0V (LOW) and +5V (HIGH).

- It has two important parameters:

- **Time Period (T)**: Duration of one complete cycle (HIGH + LOW).

- **Frequency (f)**: Number of cycles per second. ( $f = \frac{1}{T}$ )

- **Duty Cycle (D)**: Ratio of HIGH time to the total time period, expressed as a percentage.

#### Example:

- If the HIGH period = 5 ms and LOW period = 5 ms  $\rightarrow$  Total T = 10 ms

- Frequency = 100 Hz

- Duty cycle = 50%

---

## 4. Generation of TTL Clock

TTL clock signals can be generated using:

1. **Crystal Oscillator** – provides a stable frequency.

2. **555 Timer IC in Astable Mode** – generates square wave pulses.

3. **Ring Oscillator or Logic Gates** – simple clock generation.

4. **Microcontrollers / Microprocessors** – built-in clock generators.

---

## 5. Characteristics of TTL Clock

- Operates on **5V supply**.

- Produces a **clean square waveform**.

- Provides **synchronization** for sequential circuits.

- Frequency can range from a few Hz to several MHz depending on the design.

- Compatible with TTL logic circuits (74xx family).

---

## 6. Applications of TTL Clock in Digital Logic

- **Flip-Flops:** Edge-triggered devices need clock pulses for storing data.

- **Counters:** Count pulses according to clock cycles.

- **Registers:** Shift or store data with each clock pulse.

- **Microprocessors & Microcontrollers:** Require clock for instruction execution.

- **Timers & Control Circuits:** Use clock for scheduling events.

---

### Summary

- A **TTL Clock** is a periodic square waveform with voltage levels defined by TTL logic (0V = LOW, 5V = HIGH).

- It is the **heartbeat** of digital systems, ensuring all components work in synchrony.

- Essential in **flip-flops, counters, registers, microprocessors, and timing circuits**.

The **555 Timer** IC got its name from the three  $5K\Omega$  resistors that are used in its voltage divider network. This IC is useful for generating accurate time delays and oscillations. This chapter explains about 555 Timer in detail.

## Pin Diagram and Functional Diagram

In this section, first let us discuss about the pin diagram of 555 Timer IC and then its functional diagram.

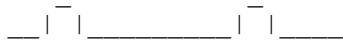

### Pin Diagram

The 555 Timer IC is an 8 pin mini Dual-Inline Package (DIP). The **pin diagram** of a 555 Timer IC is shown in the following figure –

The significance of each pin is self-explanatory from the above diagram. This 555 Timer IC can be operated with a DC supply of +5V to +18V. It is mainly useful for generating **non-sinusoidal** wave forms like square, ramp, pulse & etc

## Functional Diagram

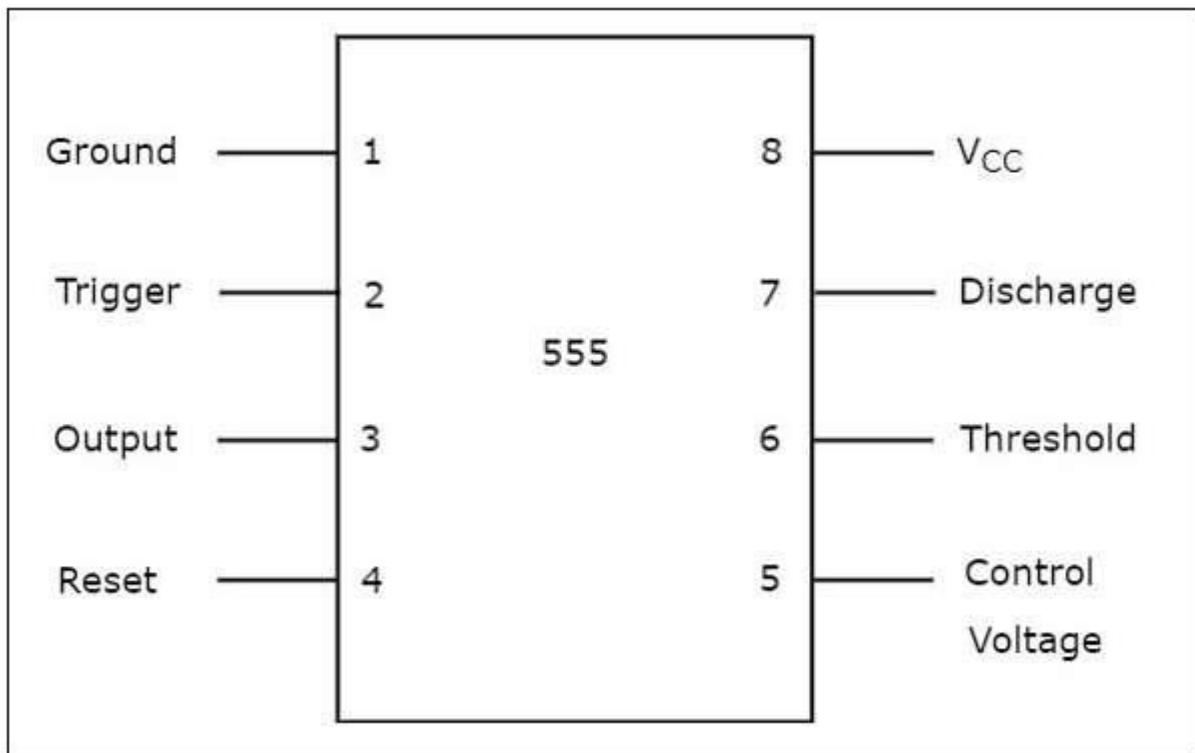

The pictorial representation showing the internal details of a 555 Timer is known as functional diagram.

The **functional diagram** of 555 Timer IC is shown in the following figure –

Observe that the functional diagram of 555 Timer contains a voltage divider network, two comparators, one SR flip-flop, two transistors and an inverter. This section discusses about the purpose of each block or component in detail –

## Voltage Divider Network

- The voltage divider network consists of a three  $5K\Omega$  resistors that are connected in series between the supply voltage  $V_{cc}$  and ground.

- This network provides a voltage of  $V_{cc/3}$  between a point and ground, if there exists only one  $5K\Omega$  resistor. Similarly, it provides a voltage of  $2V_{cc/3}$  between a point and ground, if there exists only two  $5K\Omega$  resistors.

## Comparator

- The functional diagram of a 555 Timer IC consists of two comparators: an Upper Comparator (UC) and a Lower Comparator (LC).

- Recall that a **comparator** compares the two inputs that are applied to it and produces an output.

- If the voltage present at the non-inverting terminal of an op-amp is greater than the voltage present at its inverting terminal, then the output of comparator will be  $+V_{sat}$ . This can be considered as **Logic High** ('1') in digital representation.

- If the voltage present at the non-inverting terminal of op-amp is less than or equal to the voltage at its inverting terminal, then the output of comparator will be  $-V_{sat}$ . This can be considered as **Logic Low** ('0') in digital representation.

## SR Flip-Flop

- Recall that a **SR flip-flop** operates with either positive clock transitions or negative clock transitions. It has two inputs: S and R, and two outputs:  $Q(t)$  and  $Q(t)$ . The outputs,  $Q(t)$  &  $Q(t)$  are complement to each other.

- The following table shows the **state table** of a SR flip-flop

| S | R | $Q(t+1)$ |

|---|---|----------|

| 0 | 0 | $Q(t)$   |

| 0 | 1 | 0        |

| 1 | 0 | 1        |

| 1 | 1 | -        |

- Here,  $Q(t)$  &  $Q(t+1)$  are present state & next state respectively. So, SR flip-flop can be used for one of these three functions such as Hold, Reset & Set based on the input conditions, when positive (negative) transition of clock signal is applied.

- The outputs of Lower Comparator (LC) and Upper Comparator (UC) are applied as **inputs of SR flip-flop** as shown in the functional diagram of 555 Timer IC.

## Transistors and Inverter

- The functional diagram of a 555 Timer IC consists of one npn transistor  $Q_1$  and one pnp transistor  $Q_2$ . The npn transistor  $Q_1$  will be turned ON if its base to emitter voltage is positive and greater than cut-in voltage. Otherwise, it will be turned-OFF.

- The pnp transistor  $Q_2$  is used as **buffer** in order to isolate the reset input from SR flip-flop and npn transistor  $Q_1$ .

- The **inverter** used in the functional diagram of a 555 Timer IC not only performs the inverting action but also amplifies the power level.

The 555 Timer IC can be used in mono stable operation in order to produce a pulse at the output. Similarly, it can be used in astable operation in order to produce a square wave at the output.

# A Stable

## 1. Definition

- An **Astable Multivibrator** is a **free-running oscillator** that continuously switches between two states (HIGH and LOW) without any external trigger.

- It does **not have a stable state**, hence called “astable.”

- Produces a **continuous square wave output** used as a clock pulse in digital circuits.

---

## 2. Working Principle

- The circuit uses **capacitor charging and discharging** to toggle output between HIGH and LOW.

- When the capacitor voltage reaches the **upper threshold**, output goes LOW.

- When the capacitor voltage reaches the **lower threshold**, output goes HIGH.

- This cycle repeats indefinitely, generating a square wave.

---

## 3. Astable 555 Timer Circuit

- The **555 Timer IC** is widely used to build an astable multivibrator.

- **Connections:**

- **R1** → between Vcc and pin 7 (Discharge)

- **R2** → between pin 7 (Discharge) and pin 6/2 (Threshold/Trigger)

- **C** → between pin 6/2 and ground

- **Pin 3** gives the **square wave output**.

---

## 4. Timing Calculations

Let:

- **R1, R2** = Resistors in ohms ( $\Omega$ )

- **C** = Capacitor in farads (F)

- **High Time (T\_H):**

$$T_H = 0.693 \times (R1 + R2) \times C$$

- **Low Time (T\_L):**

$$T_L = 0.693 \times R2 \times C$$

- **Total Period (T):**

$$T = T_H + T_L = 0.693 \times (R1 + 2R2) \times C$$

- **Frequency (f):**

$$f = \frac{1}{T} = \frac{1.44}{(R1 + 2R2) \times C}$$

- **Duty Cycle (D):**

$$D = \frac{T_H}{T} \times 100 = \frac{R1 + R2}{R1 + 2R2} \times 100\%$$

Note: Duty cycle is usually greater than 50% unless modified using diodes.

---

## 5. Characteristics of Astable Multivibrator

- No stable state → output continuously oscillates.

- Produces a square waveform.

- Frequency and duty cycle depend on **R1, R2, and C**.

- Can drive TTL and CMOS logic circuits.

---

## 6. Applications

- **Clock pulse generator** for digital circuits.

- **LED flashers and lamp blinkers.**

- **Tone generators and alarms.**

- **PWM (Pulse Width Modulation) circuits.**

- **Timing and waveform generation in microcontrollers.**

---

### ✓ Summary

- An **Astable Multivibrator** produces continuous square waves without any external trigger.

- When implemented with a **555 Timer**, it's a versatile clock generator used in digital logic applications.

- Its **frequency and duty cycle** can be easily adjusted using resistors and capacitors.

## UNIT IV

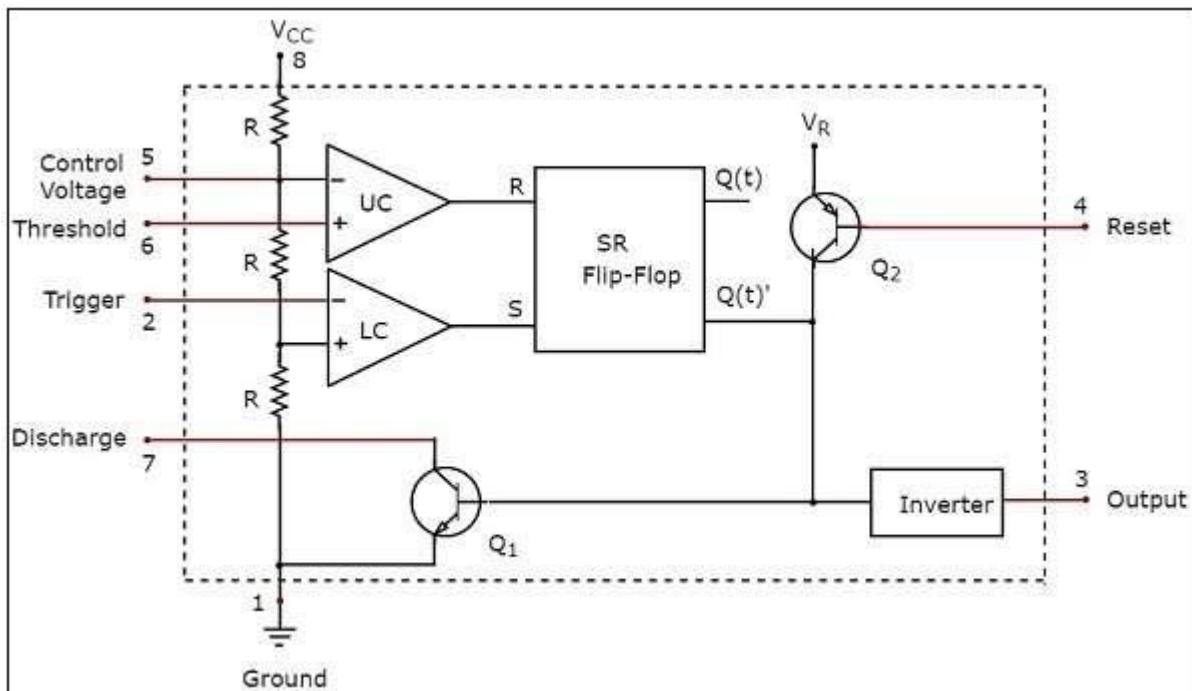

### RS flip-flop

The RS flip-flop is used to store binary information (i.e. 0 or 1). It consists of two inputs, SET and RESET. In RS flip-flop 'R' Stands for RESET and 'S' stands for SET. The flip-flop keeps its present state even when one or both inputs are deactivated. The flip-flop enters the '0' state when the RESET input is activated, and the '1' state when the SET input is activated.

The block diagram of the RS flip-flop is shown above. Since RS flip-flops are used for storing binary information it is used in simple digital applications like data registers and memory cells that require binary storage. Nevertheless, more sophisticated flip-flop designs, such as the [D flip-flop](#) or [JK flip-flop](#), are frequently used over the RS flip-flop for their increased reliability and versatility in complex digital systems due to restrictions in handling specific input conditions.

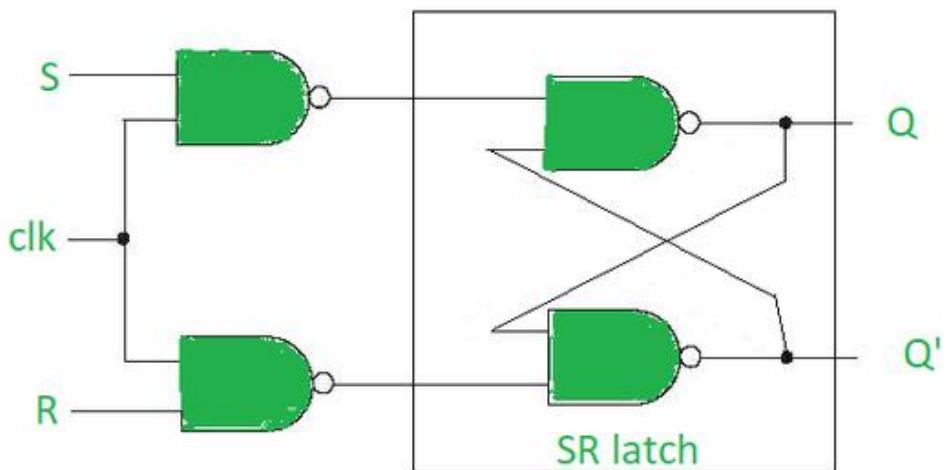

### Construction and Working of RS flip flop

RS flip can be constructed using basic [logic gates](#) such as NAND gates or NOR gates. Below shown a RS flip-flop constructed using a NAND gate same we can construct a RS flip flop using a NOR gate.

Working of RS flip-flop depends on its inputs.

- In initial state output can in any state SET or RESET.

- In SET , S=1 and R=0.

- Conversely in RESET , S=0 and R=1.

- When R=0 and S=0 it hold the current state

- When R=1 and S=1 it falls under Undefined / Forbidden state

### RS flip-flop Using NAND gates

RS flip-flop

The RS flip-flop can be constructed using 4 two input NAND gate which is shown in the above figure.

Truth Table For RS Flip-flop

| Sl no. | Clock | S | R | Q <sub>n+1</sub>            |

|--------|-------|---|---|-----------------------------|

| 1      | 0     | X | X | Q <sub>n</sub>              |

| 2      | 1     | 0 | 0 | No change                   |

| 3      | 1     | 0 | 1 | 0                           |

| 4      | 1     | 1 | 0 | 1                           |

| 5      | 1     | 1 | 1 | Undefined / Forbidden state |

Here, **S** is the Set input, **R** is the reset input, **Q<sub>n+1</sub>** is the next state and **State** tells in which state it enters

Characteristic Table For RS Flip-flop

The characteristic equation tells us about what will be the next state of flip flop in terms of present state.

| Sl no. | Q <sub>n</sub> | S | R | Q <sub>n+1</sub> |

|--------|----------------|---|---|------------------|

| 1      | 0              | 0 | 0 | 0                |

| Sl no. | Q <sub>n</sub> | S | R | Q <sub>n+1</sub> |

|--------|----------------|---|---|------------------|

| 2      | 0              | 0 | 1 | 0                |

| 3      | 0              | 1 | 0 | 1                |

| 4      | 0              | 1 | 1 | X                |

| 5      | 1              | 0 | 0 | 1                |

| 6      | 1              | 0 | 1 | 0                |

| 7      | 1              | 1 | 0 | 1                |

| 8      | 1              | 1 | 1 | X                |

Characteristic Equation :  $Q_{n+1} = S + Q_n \cdot R'$

Here, **S** is the Set input, **R** is the reset input, **Q<sub>n</sub>** is the current state input and **Q<sub>n+1</sub>** is the next state outputs.

### Excitation table For RS Flip-flop

Excitation Table basically tells about the excitation which is required by flip flop to go from current state to next state.

| Sl no. | Q <sub>n</sub> | Q <sub>n+1</sub> | S | R |

|--------|----------------|------------------|---|---|

| 1      | 0              | 0                | 0 | X |

| 2      | 0              | 1                | 1 | 0 |

| 3      | 1              | 0                | 0 | 1 |

| 4      | 1              | 1                | X | 0 |

Here, **Q<sub>n</sub>** is the current state, **Q<sub>n+1</sub>** is the next state outputs and **S, R** are the set and reset inputs respectively.

### Applications of RS Flip-flop

RS flipflop are data storage device used to store binary information. It is used in mainly devices requires binary information. Its used in:

1. Asynchronous Counters (RS flipflops are used in building the asynchronous counters ).

2. [Shift Registers](#) (RS flip-flops can be used to build shift registers).

3. State Machines.

4. Debouncing Circuit (used in stabilizing output of a switch/button).

5. Address Decoding.

6. Clock Synchronization.

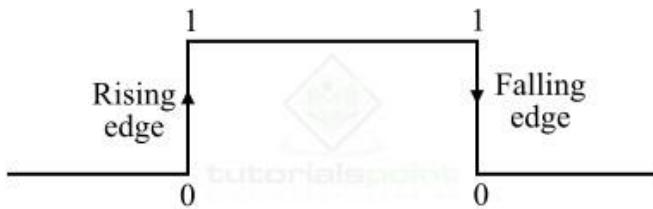

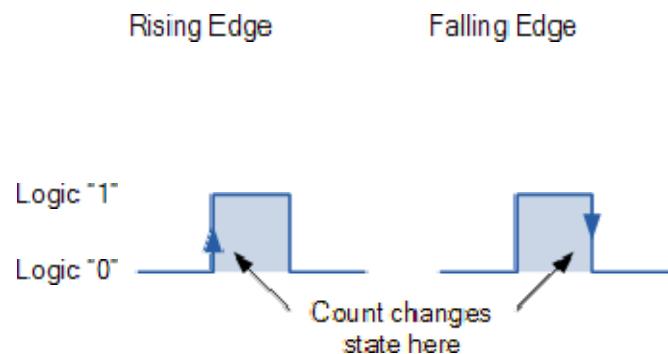

### Edge-Triggered Flip-Flop

The type of digital circuit which is capable of storing 1-bit of information and responds only when a specific edge of the clock pulse occurs is known as an **edge-triggered flip-flop**.

Therefore, the output state of the edge-triggered flip flop updates only when a specific edge of the clock pulse occurs, i.e. the clock pulse goes from either low to high or high to low states. This flip flop does not respond to a continuous clock pulse.

Edge-triggered flip-flop are used in several digital circuits where the output of the flip flop should be updated when the clock pulse changes its state from 0 to 1 or 1 to 0 as shown in Figure-2.

Figure 2 - Clock Pulse Changes State from 0 to 1 or 1 to 0

Hence, the edge triggered flip flop operates only on the rising or falling edge of the clock pulse.

#### Types of Edge-Triggered Flip-Flop

Depending on the responding edge of the clock pulse, the edge-triggered flip flops are classified into two types namely,

- Positive Edge-Triggered Flip-Flop

- Negative Edge-Triggered Flip-Flop

#### Positive Edge-Triggered Flip-Flop

The type of edge-triggered flip-flop whose output changes its state only on the rising edge (edge that goes from low to high) of the clock pulse is called a **positive edge-triggered flip-flop**. The positive edge triggered flip flop is also called a **rising edge-triggered flip-flop**. The block diagram of a positive edge triggered flip flop is shown in Figure-3 below.

Figure 3 - Positive Edge-Triggered Flip-Flop

In a positive edge triggered flip flop, the inputs are accepted and stored only when the clock pulse goes from low (0) to high (1), i.e. on the rising edge of the clock pulse. This stored value is then available on the outputs.

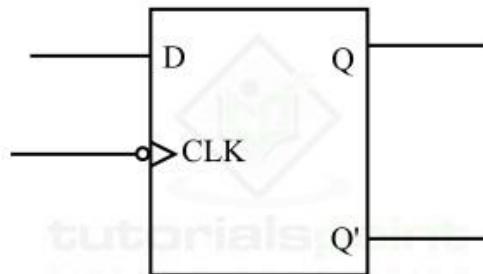

#### Negative Edge-Triggered Flip-Flop

The type of edge-triggered flip flop whose output changes its state only on the falling edge (edge that goes from high to low) of the clock pulse is called a **negative edge-triggered flip-flop**. The negative edge triggered flip flop is also known as a **falling edge-triggered flip-flop**. The block diagram of a negative edge triggered flip flop is shown in Figure-4 below.

Figure 4 - Negative Edge-Triggered Flip-Flop

In the case of negative edge triggered flip flop, the flip-flop captures and stores the inputs only when the clock pulse goes from high to low, i.e. on falling edge of the clock pulse.

#### Operation of Edge-Triggered Flip-Flop

The operation of a typical edge-triggered flip-flop is described below

In the edge-triggered flip-flop, the inputs are applied through the input terminals and a clock pulse is connected to the clock input of the flip-flop. The edge triggered flip flop responds according to the applied inputs when the clock pulse goes from either low to high or high to low. When this state transition of clock pulse occurs, the flip-flop captures and stores the input values. These stored input values will be then available on the outputs (Q and Q') of the flip-flop.

#### Advantages of Edge-Triggered Flip-Flop

The important advantages of the edge-triggered flip flop are listed as follows

- Edge triggered flip flops have an improved timing behavior as compared to the level triggered flip flops. This is because, the edge triggered flip flop responds only on the transition of clock pulse.

- Edge-triggered flip flops reduces the possibility of glitches that cause errors in the system.

- Edge triggered flip flops consumes relative low power than the level-triggered flip flops.

- Edge-triggered flip flop has relatively less complex circuit design.

- Edge triggered flip flops can be easily integrated in the form of digital ICs.

- Edge triggered flip flops are very useful in digital systems having very high clock speed.

#### Applications of Edge-Triggered Flip-Flop

Edge triggered flip flops are used in a variety of digital systems. Some common applications of edge triggered flip flops are –

- Edge triggered flip-flops are used in registers to store and transfer binary information among different parts of a digital circuit.

- Edge triggered flip flops are used in digital counters for generating sequences of binary values.

- Edge triggered flip flops are also used for digital signal processing.

- Edge triggered flip flops are used in several digital applications where timing and signal synchronization is required.

- Edge-triggered flip flops are also used to build memory cells of ROM, RAM, etc. to stores binary data in a digital system.

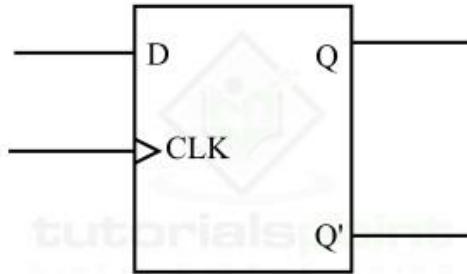

#### Edge Triggered D Flip Flops

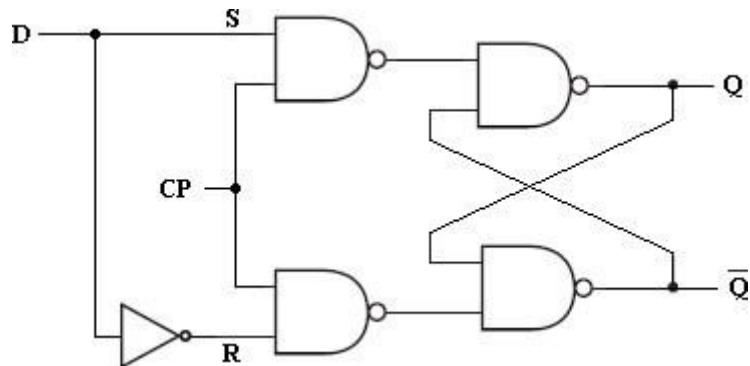

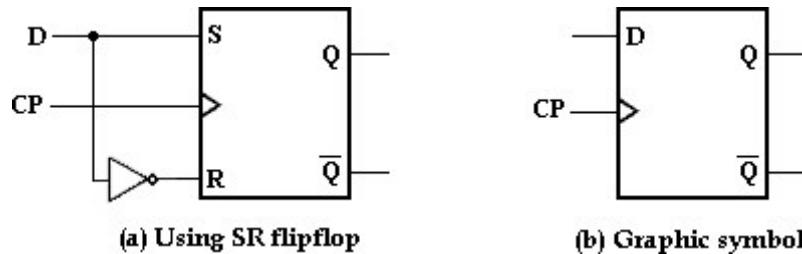

Like in D latch, in D Flip-Flop the basic SR Flip-Flop is used with complemented inputs.

The D Flip-Flop is similar to D-latch except clock pulse is used instead of enable input.

Fig : 3.18 - D Flip-Flop

To eliminate the undesirable condition of the indeterminate state in the RS Flip-Flop is to ensure that inputs S and R are never equal to 1 at the same time. This is done by D Flip-Flop. The D (**delay**) Flip-Flop has one input called delay input and clock pulse input. The D Flip-Flop using SR Flip-Flop is shown below.

Fig : 3.19 – D Flipflop using SR Flipflop The truth table of D Flip-Flop is given below.

| Clock | D | Q <sub>n+1</sub> | State     |

|-------|---|------------------|-----------|

| 1     | 0 | 0                | Reset     |

| 1     | 1 | 1                | Set       |

| 0     | x | Q <sub>n</sub>   | No Change |

Truth table for D Flip-Flop

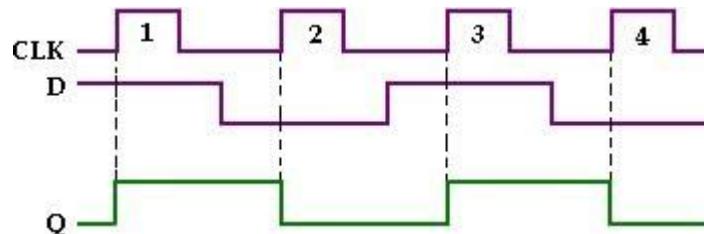

Fig : 3.20 - Input and output waveforms of clocked D Flip-Flop

Looking at the truth table for D Flip-Flop we can realize that  $Q_{n+1}$  function follows the D input at the positive going edges of the clock pulses.

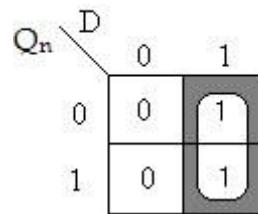

#### Characteristic table and Characteristic equation:

The characteristic table for D Flip-Flop shows that the next state of the Flip- Flop is

independent of the present state since  $Q_{n+1}$  is equal to D. This means that an input pulse will transfer the value of input D into the output of the Flip-Flop independent of the value of the output before the pulse was applied. The characteristic equation is derived from K-map.

| $Q_n$ | D | $Q_{n+1}$ |

|-------|---|-----------|

| 0     | 0 | 0         |

| 0     | 1 | 1         |

| 1     | 0 | 0         |

| 1     | 1 | 1         |

Characteristic table

K-map simplification

Characteristic equation:  $Q_{n+1} = D$ .

### Edge Triggered JK Flip Flops

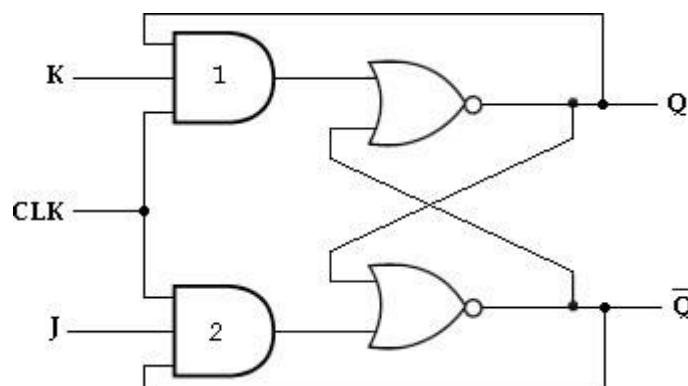

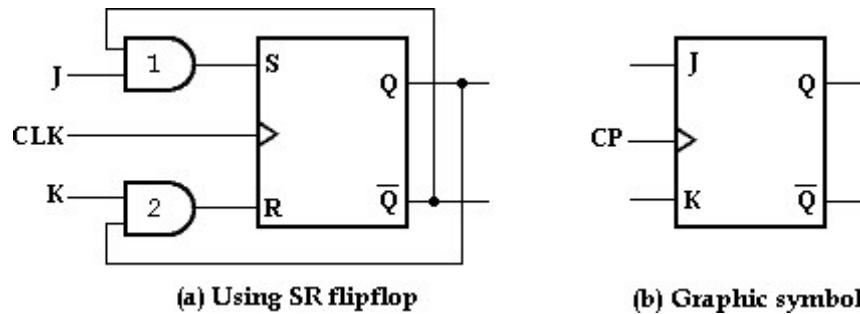

JK means Jack Kilby, Texas Instrument (TI) Engineer, who invented IC in 1958. JK Flip-Flop has two inputs J(set) and K(reset). A JK Flip-Flop can be obtained from the clocked SR Flip-Flop by augmenting two AND gates as shown below.

Fig : 3.15 - JK Flip Flop

The data input J and the output  $Q'$  are applied to the first AND gate and its output ( $JQ'$ ) is applied to the S input of SR Flip-Flop. Similarly, the data input K and the output Q are applied to the second AND gate and its output ( $KQ$ ) is applied to the R input of SR Flip-Flop.

Fig : 3.16 – JK Flipflop using SR Flipflop

**J= K= 0**

When  $J=K= 0$ , both AND gates are disabled. Therefore clock pulse have no effect, hence the Flip-Flop output is same as the previous output.

**J= 0, K= 1**

When  $J= 0$  and  $K= 1$ , AND gate 1 is disabled i.e.,  $S= 0$  and  $R= 1$ . This condition will reset the Flip-Flop to 0.

**J= 1, K= 0**

When  $J= 1$  and  $K= 0$ , AND gate 2 is disabled i.e.,  $S= 1$  and  $R= 0$ . Therefore the Flip-Flop will set on the application of a clock pulse.

**J= K= 1**

When  $J=K=1$ , it is possible to set or reset the Flip-Flop. If  $Q$  is High, AND gate 2 passes on a reset pulse to the next clock. When  $Q$  is low, AND gate 1 passes on a set pulse to the next clock. Eitherway,  $Q$  changes to the complement of the last state i.e., toggle. Toggle means to switch to the opposite state.

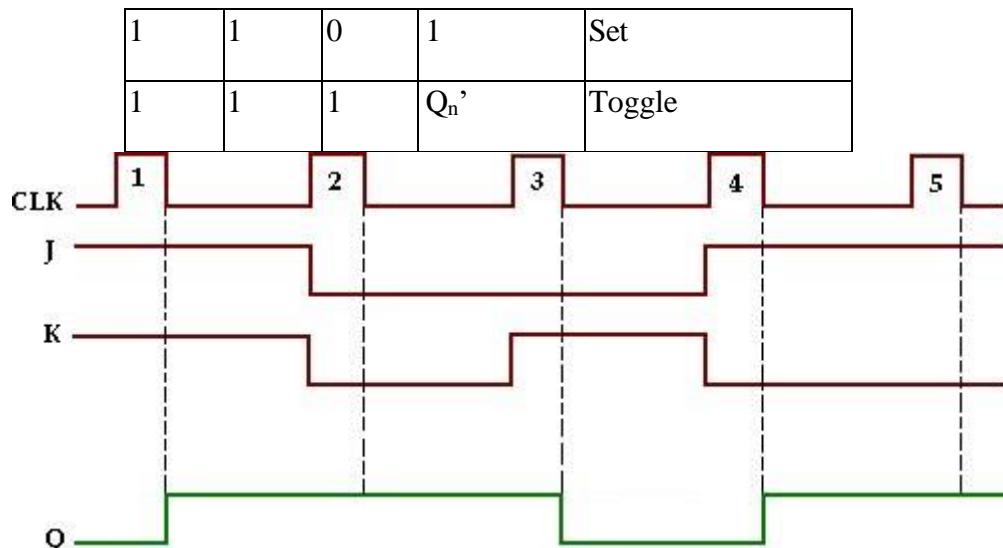

The truth table of JK Flip-Flop is given below.

| CLK | Inputs |   | Output<br>$Q_{n+1}$ | State     |

|-----|--------|---|---------------------|-----------|

|     | J      | K |                     |           |

| 1   | 0      | 0 | $Q_n$               | No Change |

| 1   | 0      | 1 | 0                   | Reset     |

Fig : 3.17 - Input and output waveforms of JK Flip-Flop

#### Characteristic table and Characteristic equation:

The characteristic table for JK Flip-Flop is shown in the table below. From the table, K-map for the next state transition ( $Q_{n+1}$ ) can be drawn and the simplified logic expression which represents the characteristic equation of JK Flip-Flop can be found.

| $Q_n$ | J | K | $Q_{n+1}$ |

|-------|---|---|-----------|

| 0     | 0 | 0 | 0         |

| 0     | 0 | 1 | 0         |

| 0     | 1 | 0 | 1         |

$$\left| \begin{array}{cc|cc|c} 0 & 1 & 1 & 1 & \\ 1 & 0 & 0 & 1 & \\ 1 & 0 & 1 & 0 & \\ 1 & 1 & 0 & 1 & \\ 1 & 1 & 1 & 0 & \end{array} \right|$$

### K-map Simplification:

| $Q_n$ | $J$ | $K$ | 00 | 01 | 11 | 10 |

|-------|-----|-----|----|----|----|----|

| 0     | 0   | 0   | 0  | 0  | 1  | 1  |

| 1     | 1   | 0   | 1  | 0  | 0  | 1  |

Characteristic equation:  $Q_{n+1} = JQ' + K'Q$ .

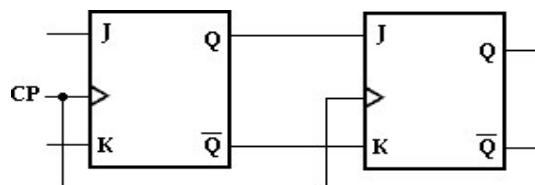

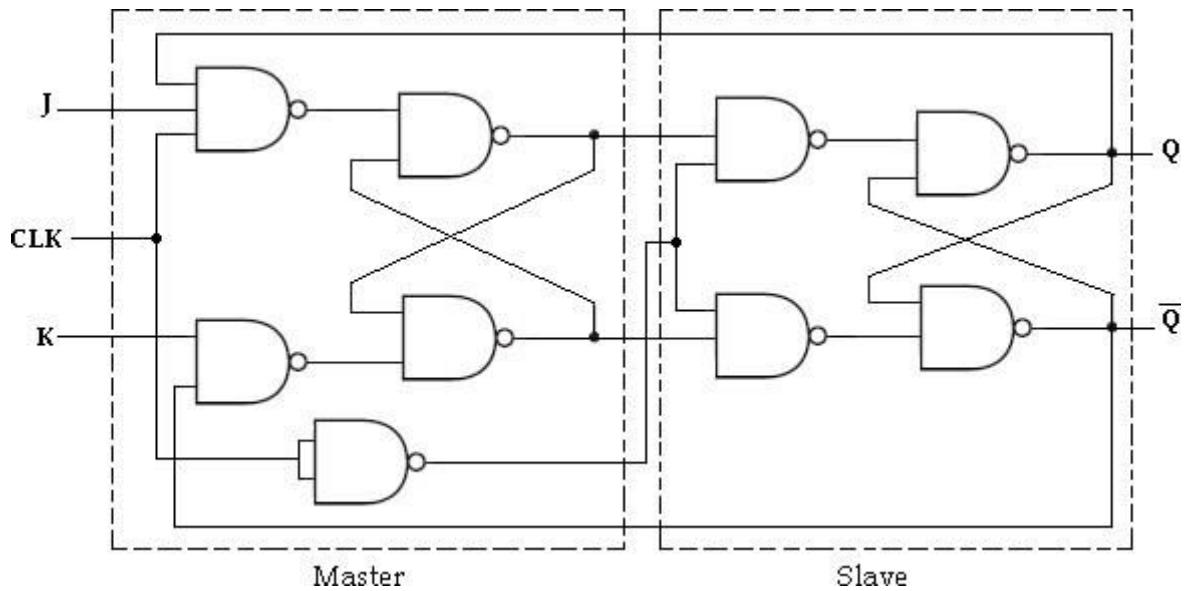

### **JK Master Slave Flip Flops**

A master-slave Flip-Flop is constructed using two separate JK Flip-Flops. The first Flip-Flop is called the master. It is driven by the positive edge of the clock pulse. The second Flip-Flop is called the slave. It is driven by the negative edge of the clock pulse. The logic diagram of a master-slave JK Flip-Flop is shown below.

Fig : 3.32 - Logic diagram

When the clock pulse has a positive edge, the master acts according to its J- K inputs, but the slave does not respond, since it requires a negative edge at the clock input.

When the clock input has a negative edge, the slave Flip-Flop copies the master outputs. But the master does not respond since it requires a positive edge at its clock input. The clocked master-slave J-K Flip-Flop using NAND gates is shown below.

Fig : 3.33 - Master-Slave JK Flip-Flop

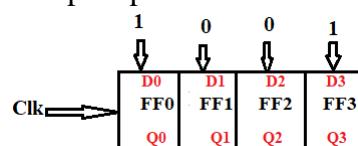

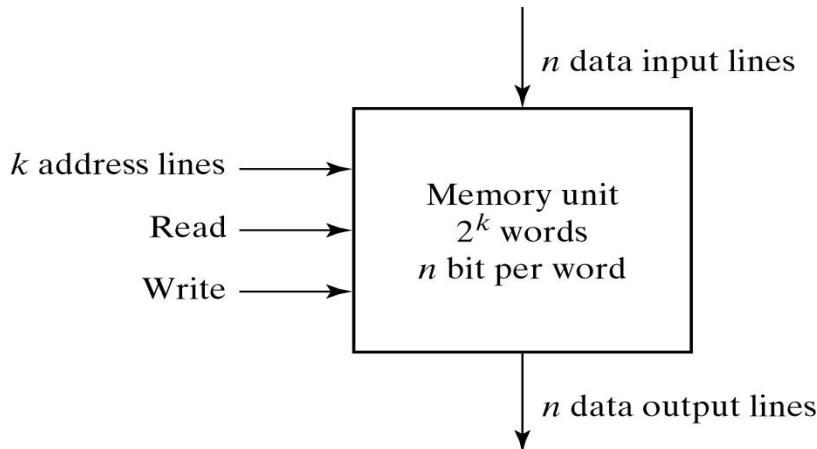

## Register

A single flip-flop is able to store single bit information either 0 or 1, but to store more than one bit information, a group of flip-flops need to be connected. A group of flip-flops is called a register. If a register contains  $n$  flip-flops, it is able to store  $n$  bit information. Registers can be used to generate the specified sequence and can also be used to shift the content of flip-flop position wise, based on this the applications of registers are classified into two categories.

1. Shift registers and

2. Counters

### 1. Shift registers

A shift register is an entity of flip-flops, which are capable of shifting the state of flip-flop positionwise in one direction or two directions.

**Example:** To store 4-bit data 1001, four flip-flops are used.

Figure 32: Basic shift register

Based on the direction of shifting the content of flip-flop, shift registers are classified into two types.

a) *Unidirectional shift registers*

The unidirectional shift registers, shifts the contents of flip-flops in only one direction

either right shift or left shift.

**b) Bidirectional shift registers**

The Bidirectional shift registers are capable of performing right shift as well as left shift through a proper control signal.

**c) Universal shift register**

The universal shift registers are capable of performing right shift as well as left shift through a proper control signal along with parallel loading and memory.

Shift registers further classified into four types, based on the way the input is loaded and the output is received.

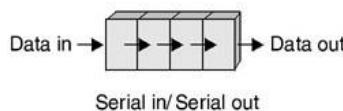

**a) Serial input and serial output**

The information will be loaded serially through a single line and output will be received serially through a single line is called serial input and serial output (SISO) shift register shown in figure (33).

Figure 33: SISO Shift register

**b) Serial input and parallel output**

the information will be loaded serially through a single line and output will be received in parallel through multiple lines is called serial input parallel output (SIPO) shift register

shown in figure (34).

Figure 34: SIPO Shift register

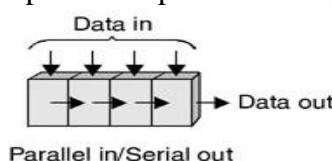

**c) Parallel input and serial output**

The information bits will be loaded in parallel through multiple lines and output will be received through a single line is called parallel input serial output (PISO) shift register

shown in figure (35).

Figure 35: SISO Shift register

#### d) Parallel input and parallel output

The information bits will be loaded in parallel through multiple lines and output will be taken in parallel with multiple output lines is called parallel input parallel output (PIPO) shift register shown in figure (36).

Figure 36: SISO Shift register

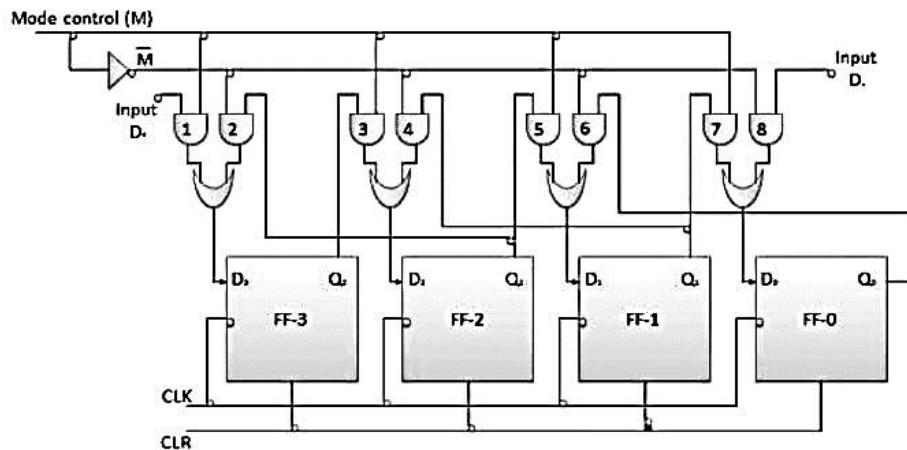

#### Bidirectional Shift register

Performs both left shift and right shift

$M=0$  (Shift left operation),  $M=1$  (Shift right operation)

#### Logic diagram

Figure 46: Logic diagram of bidirectional shift registers

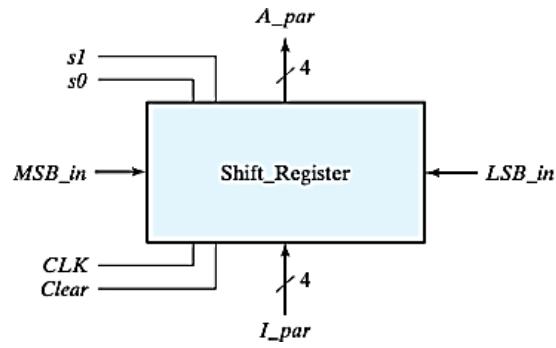

#### Universal Shift Register

Bidirectional Shift Register + (SISO, SIPO, PIPO, PISO)+Memory

Figure 47: Logic symbol of universal shift register

| <b>S1</b> | <b>S0</b> | <b>Register Operation</b> |

|-----------|-----------|---------------------------|

| 0         | 0         | No Change<br>(Memory)     |

| 0         | 1         | Shift left                |

| 1         | 0         | Shift right               |

| 1         | 1         | Parallel loading          |

Table 28: Universal shift operations table

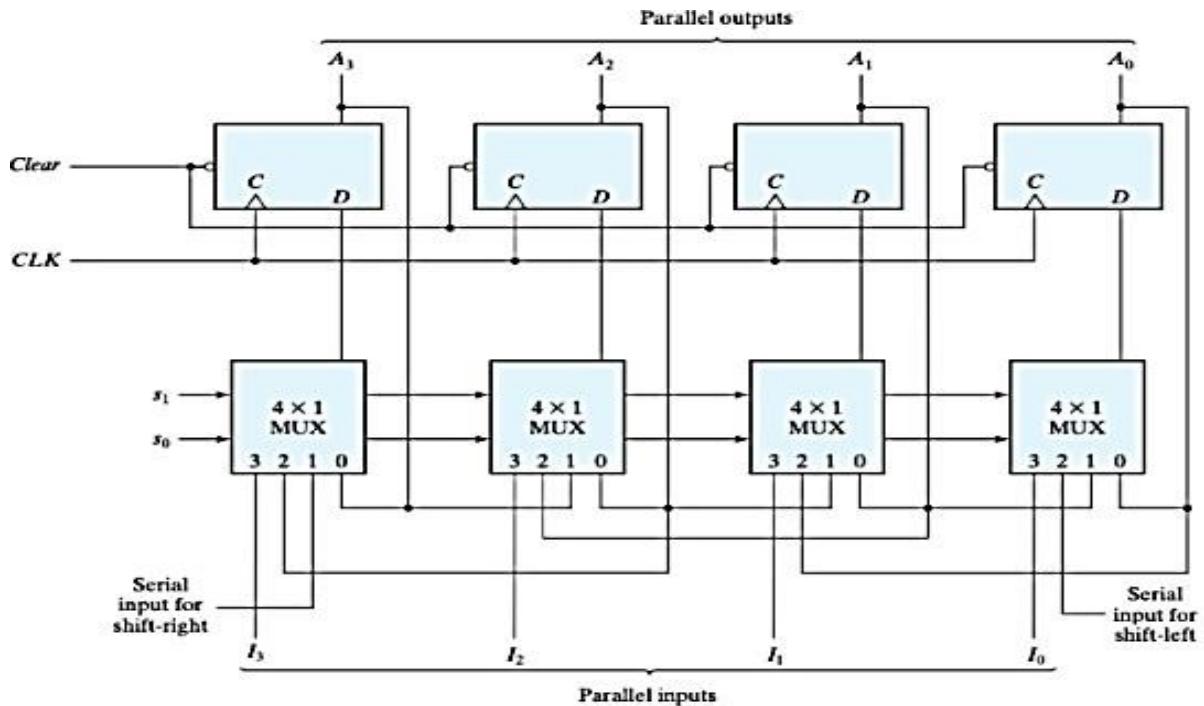

## Logic Diagram

Figure 48: Logic diagram of universal shift register

4/7/22, 12:58 PM

Ripple Counter in Digital Electronics - Javatpoint

## Ripple Counter

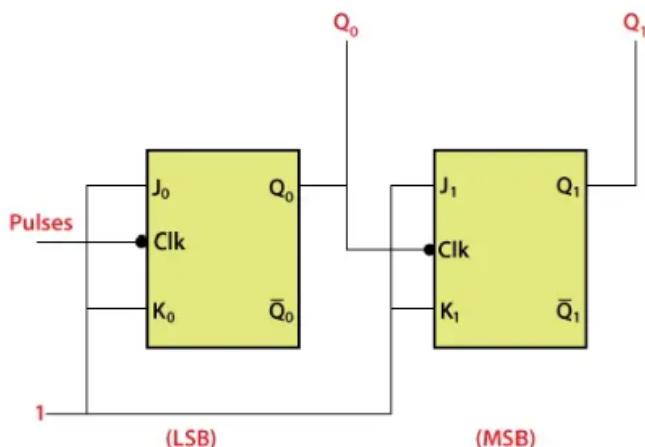

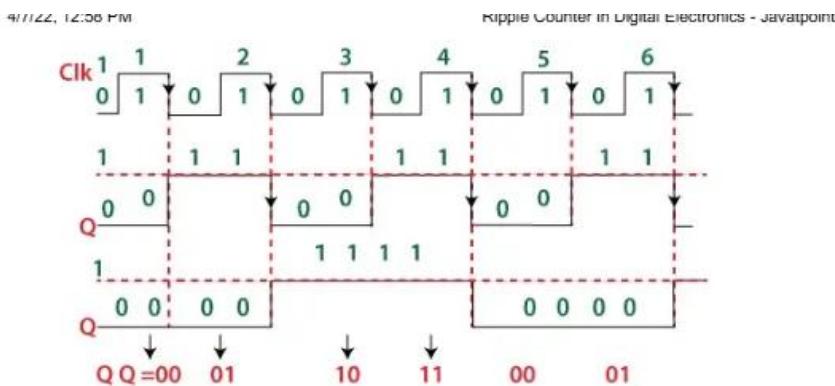

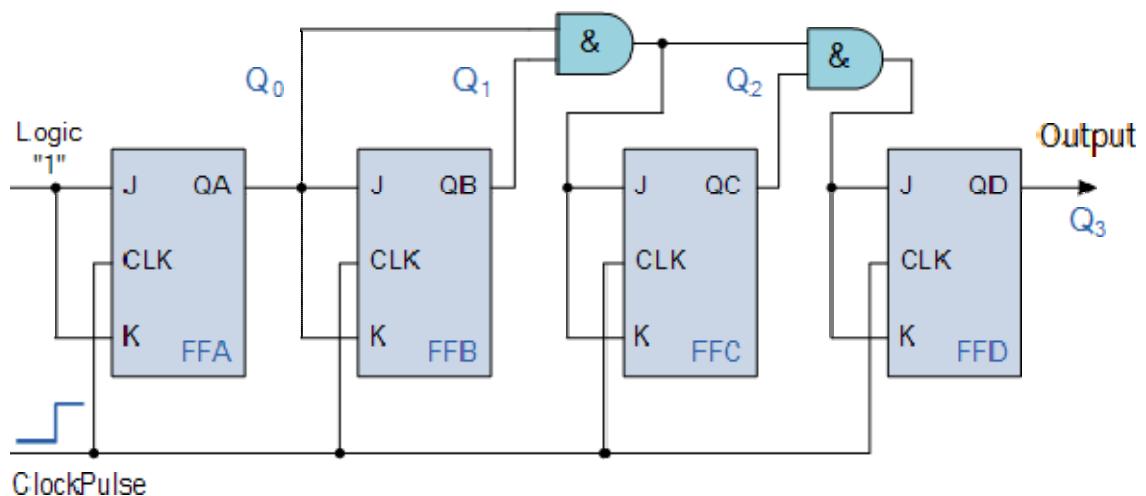

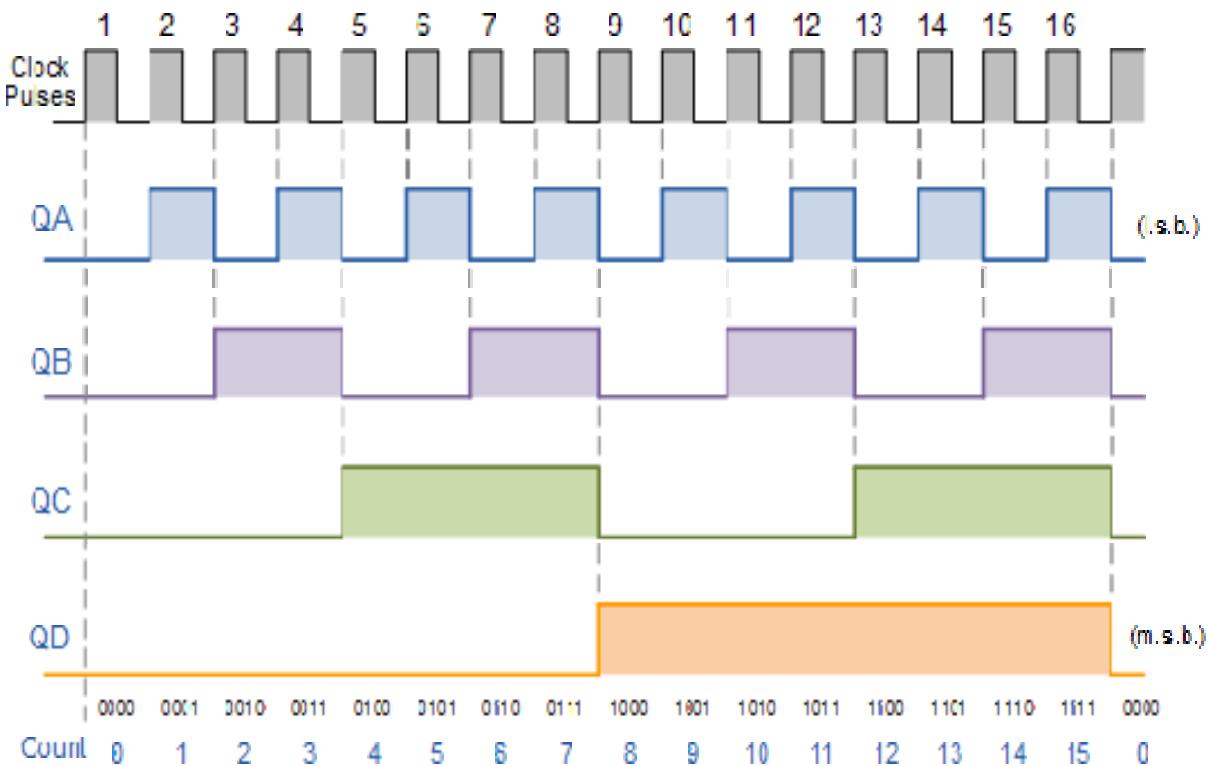

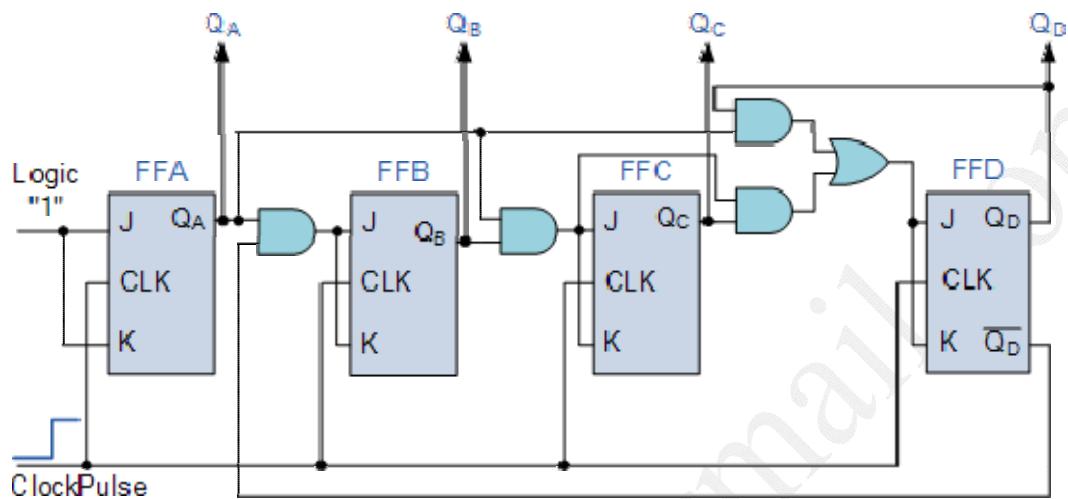

Ripple counter is a special type of **Asynchronous** counter in which the clock pulse ripples through the circuit. The  $n$ -MOD ripple counter forms by combining  $n$  number of flip-flops. The  $n$ -MOD ripple counter can count  $2^n$  states, and then the counter resets to its initial value.

### Features of the Ripple Counter:

- Different types of flip flops with different clock pulse are used.

- It is an example of an asynchronous counter.

- The flip flops are used in toggle mode.